# SURE 静岡大学学術リポジトリ Shizuoka University REpository

CMOSイメージセンサのカラム並列型低ノイズ信号 読み出し回路に関する研究

| メタデータ | 言語: ja                            |

|-------|-----------------------------------|

|       | 出版者: 静岡大学                         |

|       | 公開日: 2012-03-08                   |

|       | キーワード (Ja):                       |

|       | キーワード (En):                       |

|       | 作成者: 榊原, 雅樹                       |

|       | メールアドレス:                          |

|       | 所属:                               |

| URL   | https://doi.org/10.14945/00006434 |

| 電子科学研究科;     | ; GD      |

|--------------|-----------|

|              | K         |

| 0006506091 R | 452       |

|              | 静岡大学附属図書館 |

# 静岡大学博士論文

# CMOSイメージセンサの カラム並列型低ノイズ 信号読み出し回路に関する研究

2006年2月

静岡大学大学院電子科学研究科 ナノビジョン工学専攻

榊原雅樹

# 目次

| 第1章 | 序論                             | 1          |

|-----|--------------------------------|------------|

| 1.1 | 本研究の背景                         | 1          |

| 1.2 | 本研究の目的                         | 3          |

| 1.3 | 本論文の構成                         | 5          |

|     |                                |            |

| 第2章 | 低ノイズイメージセンサの基礎的考察              | 8          |

| 2.1 | はじめに                           | 8          |

| 2.2 | CMOS イメージセンサによる撮像              | 8          |

|     | 2.2.1 撮像の基本動作                  | 8          |

|     | 2.2.2 光電変換部                    | 8          |

|     | 2.2.3 パッシブピクセルセンサ              | 10         |

|     | 2.2.4 アクティブピクセルセンサ             | 11         |

|     | 2.2.5 埋め込みフォトダイオードと完全転送        | 12         |

|     | 2.2.6 カラムノイズキャンセル回路            | 12         |

|     | 2.2.7 A/D 変換器                  | 14         |

| 2.3 | CMOS イメージセンサのノイズ               | 15         |

|     | 2.3.1 固定パターンノイズ                | 16         |

|     | 2.3.2 熱ノイズ                     | 16         |

|     | 2.3.3 1/fノイズ                   | 17         |

|     | 2.3.4 リセットノイズ                  | 18         |

|     | 2.3.5 ショットノイズ                  | 19         |

|     | 2.3.6 量子化ノイズ                   | 19         |

|     | 2.3.7 その他のノイズ                  | 19         |

|     |                                |            |

| 第3章 | 適応ゲインカラム増幅に基づく高感度 CMOS イメージセンサ | <b>2</b> 3 |

| 3.1 | はじめに                           | 23         |

| 3.2 | 適応ゲインカラム増幅に基づく CMOS イメージセンサの構成 | 24         |

| 3.3 | 画素回路                           | 25         |

| 3.4 | 適応ゲインカラム増幅回路                   | 26         |

|     | 3.4.1 カラム増幅回路                  | 26         |

|     | 3.4.2 増幅器                      | 28         |

|     | 3.4.3 比較器                      | 30         |

|     | 3.4.4 ゲインメモリ                   | 32         |

|     | 3.4.5 S/H、バッファ部                | 32         |

| 3.5 |                                | 36         |

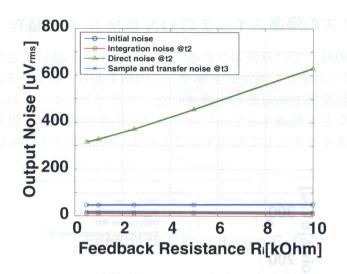

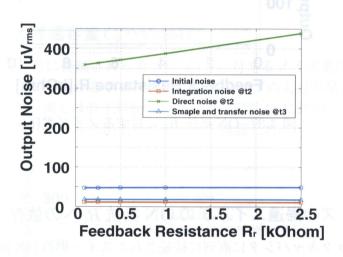

|   | 3.6  | 適応ゲインカラム増幅器のノイズの見積もり                |

|---|------|-------------------------------------|

|   |      | 3.6.1 はじめに                          |

|   |      | 3.6.2 容量 C で帯域制限されたノイズ              |

|   |      | 3.6.3 スイッチトキャパシタ回路でのノイズ             |

|   |      | 3.6.4 適応ゲインカラム増幅器のノイズの計算例           |

|   | 3.7  | 適応ゲインカラム増幅器を用いたイメージセンサの試作と特性測定 .    |

|   |      | 3.7.1 試作したイメージセンサ                   |

|   |      | 3.7.2 測定環境                          |

|   |      | 3.7.3 入出力特性の測定                      |

|   | 3.8  | 測定結果                                |

|   | 3.9  | 考察                                  |

|   | 3.10 | まとめ                                 |

|   |      |                                     |

| 第 | 4章   | 2重積分型カラム並列 A/D 変換器                  |

|   | 4.1  | はじめに                                |

|   | 4.2  | 2 重積分型 A/D 変換器の構成                   |

|   |      | 4.2.1 全体の構成                         |

|   |      | 4.2.2 2 重積分型 A/D 変換器の構成             |

|   |      | 4.2.3 2 重積分型 A/D 変換器のモード            |

|   | 4.3  | 2 重積分型 A/D 変換器の動作                   |

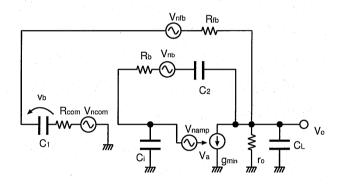

|   |      | 4.3.1 アナログ積分器と 1bitDAC の構成          |

|   |      | 4.3.2 増幅器の構成と特性                     |

|   |      | 4.3.3 比較器の構成                        |

|   |      | 4.3.4 比較器の動作                        |

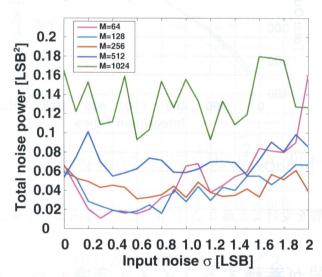

|   | 4.4  | 2重積分型 A/D 変換器の量子化ノイズ低減効果の解析         |

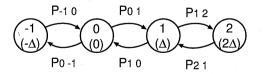

|   |      | 4.4.1 4状態での状態遷移図を用いた解析              |

|   |      | 4.4.2 状態遷移図による解析の一般化                |

|   | 4.5  | シミュレーションによる検証                       |

|   | 4.6  | ランダムノイズの見積もり                        |

|   |      | 4.6.1 ノイズ解析をする回路                    |

|   |      | 4.6.2 初期状態での回路のノイズ解析                |

|   |      | $4.6.3$ 偶数時刻 $t_2$ でのノイズ解析 $\dots$  |

|   |      | $4.6.4$ 奇数時刻 $t_3$ でのノイズ解析 $\ldots$ |

|   |      | $4.6.5$ 時刻 $t_k$ で発生するノイズ解析 $\dots$ |

|   |      | 4.6.6 アナログ積分器の積分終了時のノイズ             |

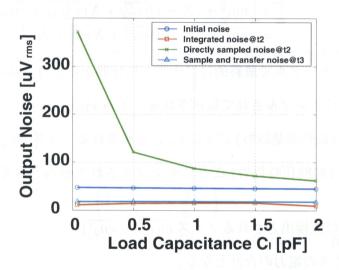

|   | 4.7  | ノイズの計算と各パラメータへの依存                   |

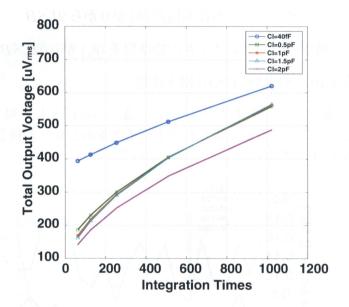

|   |      | 4.7.1 ノイズの負荷容量 C <sub>l</sub> への依存  |

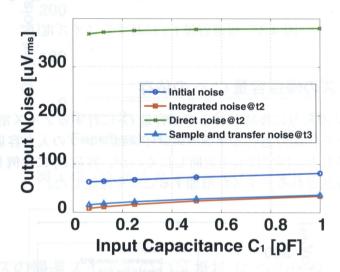

|   |      | 4.7.2 ノイズの入力容量 $C_1$ への依存           |

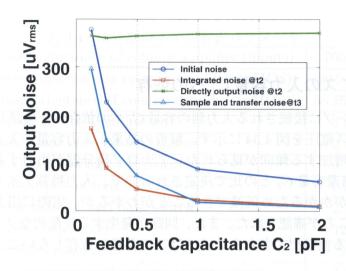

|   |      | 4.7.3 ノイズの帰還容量 C2 への依存              |

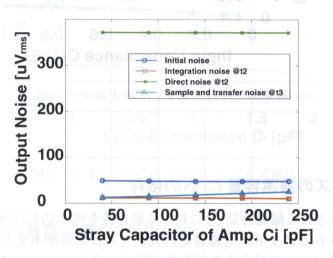

|     | 4.7.4     | ノイズの帰還容量 $C_i$ への依存 $\ldots$ | 93  |

|-----|-----------|---------------------------------------------------------------------------------------------------------------|-----|

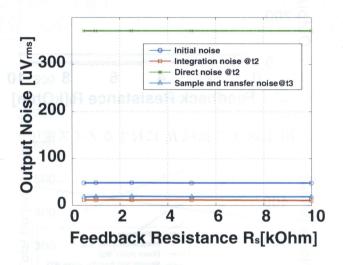

|     | 4.7.5     | ノイズの帰還スイッチの ON 抵抗 $R_s$ への依存 $\dots$                                                                          | 94  |

|     | 4.7.6     | ノイズの帰還スイッチの ON 抵抗 $R_i$ への依存 $\ldots$                                                                         | 94  |

|     | 4.7.7     | ノイズの帰還スイッチの ON 抵抗 $R_r$ への依存 $\dots$                                                                          | 94  |

|     | 4.7.8     | 積分動作により積分器に蓄積されるノイズ                                                                                           | 95  |

| 4.8 | 積分器       | が蓄積するノイズを考慮したノイズ低減効果の見積もり                                                                                     | 96  |

| 4.9 | まとめ       | )                                                                                                             | 100 |

| **  | ∖÷÷ ⊶⊷ T∃ |                                                                                                               |     |

| 第5章 |           | 貴分機能共有カラム並列巡回型 A/D 変換器                                                                                        | 103 |

| 5.1 | はじめ       |                                                                                                               | 103 |

| 5.2 |           | 行分機能共有カラム並列 1.5bit 巡回型 A/D 変換器を用いた CMOS                                                                       | 104 |

| _ ~ |           | · ジセンサの構成                                                                                                     | 104 |

| 5.3 |           | 3の構成                                                                                                          | 106 |

| 5.4 |           | 行分機能共有 1.5b 巡回型カラム A/D 変換器の構成                                                                                 | 108 |

|     | 5.4.1     | 増幅器の構成と特性・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                                                 | 109 |

|     | 5.4.2     | 比較器の構成・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                                                    | 109 |

|     | 5.4.3     | 比較器の動作・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                                                    | 109 |

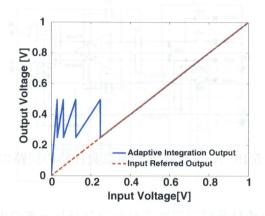

| 5.5 |           | 行分機能共有 1.5bitA/D 変換器の動作                                                                                       | 111 |

|     | 5.5.1     | 適応積分機能共有 1.5bitA/D 変換器の積分器としての動作                                                                              | 111 |

|     | 5.5.2     | 適応積分共有 1.5bitA/D 変換器の適応積分動作                                                                                   | 114 |

|     | 5.5.3     | 適応積分機能共有 1.5bit 巡回型 A/D 変換器の A/D 変換器とし                                                                        |     |

|     |           | ての動作                                                                                                          | 116 |

| 5.6 |           | {分機能共有 1.5bitA/D 変換器のシミュレーション                                                                                 | 119 |

| 5.7 | 回路の       | 誤差を考慮した適応積分と 1.5bitA/D 変換器のシミュレーション                                                                           |     |

| ,   | 5.7.1     | 適応積分器のシミュレーション                                                                                                | 122 |

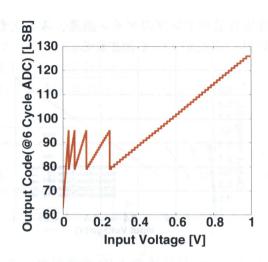

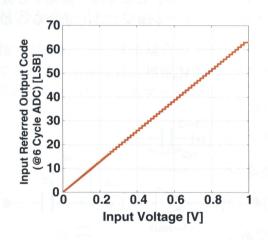

|     | 5.7.2     | 積分機能共有 1.5bit 巡回型 A/D 変換器の A/D 変換器のシミュ                                                                        |     |

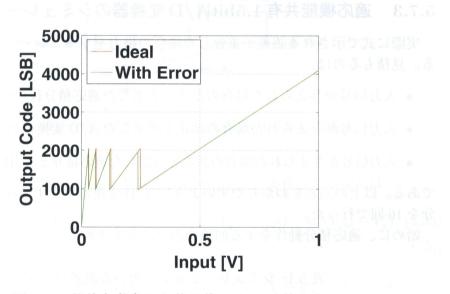

|     |           | レーション                                                                                                         | 124 |

|     | 5.7.3     | 適応機能共有 1.5bitA/D 変換器のシミュレーション                                                                                 | 126 |

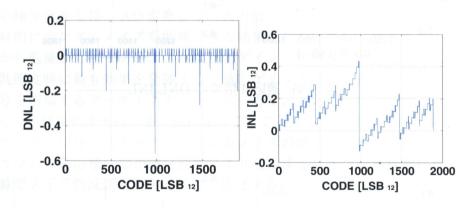

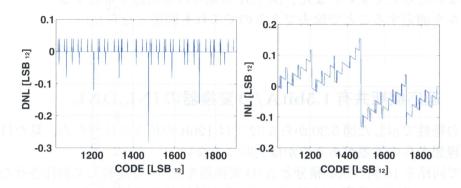

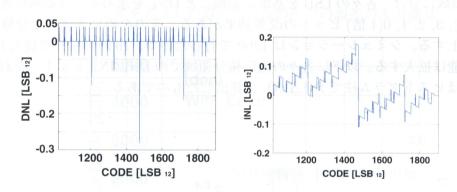

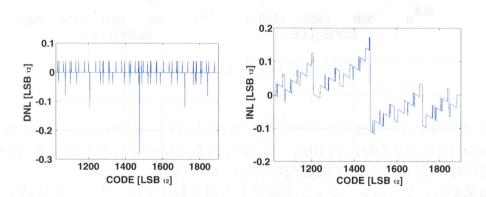

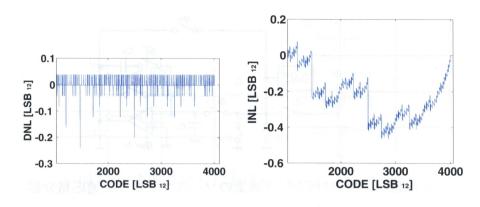

|     | 5.7.4     | 適応機能共有 1.5bitA/D 変換器の INL,DNL                                                                                 |     |

| 5.8 | 適応積       | 漬分機能共有 1.5bitA/D 変換器のノイズ解析                                                                                    |     |

|     | 5.8.1     | はじめに                                                                                                          |     |

|     | 5.8.2     | 解析する回路                                                                                                        |     |

|     | 5.8.3     | 各動作フェーズにおける等価回路                                                                                               |     |

|     | 5.8.4     | 初期状態での回路のノイズ解析                                                                                                |     |

|     | 5.8.5     | 時刻 $t_2$ でのノイズ解析                                                                                              |     |

|     | 5.8.6     | 時刻 $t_3$ でのノイズ解析                                                                                              |     |

| •   | 5.8.7     | 積分終了時でのノイズ解析                                                                                                  |     |

|     | 5.8.8     | 適応積分動作で発生するノイズ                                                                                                |     |

| 5.9 | 適応積       | 『分機能共有 1.5bitA/D 変換器の積分時のノイズの計算                                                                               | 138 |

| 論 | 文目録  | i<br>K |     |       |    |     |     |    |     |        |        |       |         |   |   |   |       |   |   |   |       | 156 |

|---|------|--------|-----|-------|----|-----|-----|----|-----|--------|--------|-------|---------|---|---|---|-------|---|---|---|-------|-----|

| 第 | 6章   | 結論     |     |       |    |     |     |    |     |        |        |       |         |   |   |   |       |   |   |   |       | 150 |

|   | 5.11 | まとめ    |     | • • • |    | • • | . • |    | •   | • , •, | •      | <br>• | ٠٠.     |   |   | ٠ | • •   | • |   | • | <br>• | 146 |

|   |      | 5.10.3 | 諸特性 | Ė.,   |    |     |     |    | . • |        | •      | <br>• | • • • • |   | • |   | . , . |   |   |   |       | 145 |

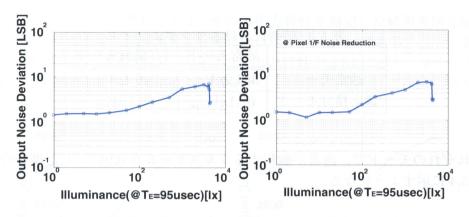

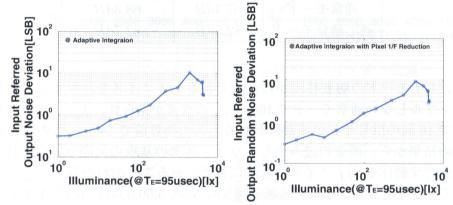

|   |      | 5.10.2 | ランタ | ブムノ   | イ, | ズ特  | 性   |    | • 1 |        | •      |       |         |   |   |   |       |   | • |   |       | 143 |

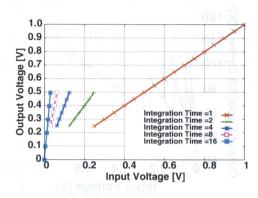

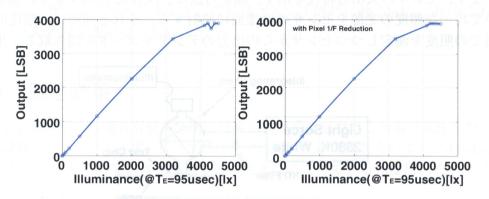

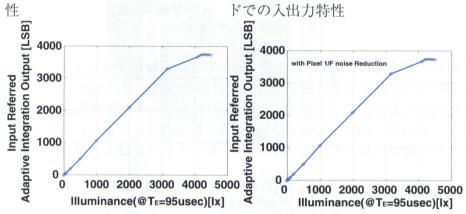

|   |      | 5.10.1 | 入出力 | J特性   | :  |     |     |    |     |        |        |       |         |   |   |   | ٠.,٠  |   |   |   |       | 142 |

|   | 5.10 | 測定結    | 果   | ·     |    |     |     |    | ٠.  | •. •   |        |       |         |   |   |   |       | • |   |   |       | 141 |

|   |      | 5.9.1  | 積分重 | が作に   | よ  | るノ  | イ.  | ズの | り但  | 玉減     | r<br>V | <br>  |         | • |   |   |       |   |   |   |       | 138 |

# 第1章

# 序論

# 1.1 本研究の背景

デジタルスチルカメラ、ビデオカメラ、セキュリティカメラ、工業用カメラ等の電子式カメラの心臓部は固体撮像素子(固体イメージセンサ)である。近年では、ネットワークインフラと一般家庭へのパーソナルコンピュータの普及とともに、その取り扱いの容易さとパーソナルコンピュータとの親和性の高さから、一般消費者にも「デジタルカメラ」という家電製品として固体撮像素子を使用したものが広く普及している。

個体撮像素子には主に、CCD(charge coupled device, 電荷結合素子) イメージセンサと CMOS(complementaly metal oxide semiconductor, 相補型金属酸化膜半導体) イメージセンサの 2 者がある。CCD は、アメリカにあるベル研究所の Willard Boyle と George Smith がその基本原理を 1969 年に考案 [1] して以来、現在に至るまでに様々な改良がなされている。開発当初は、広く使用されていた撮像管に比べて小型、計量、長寿命、耐振動などに優れていたため主にビデオカメラを中心に普及した。その後も、現在に至るまで研究開発が盛んに行われ、その高い基本特性である低ノイズ特性から質の高い画像を得ることができるため、デジタルスチルカメラを始め幅広く画像の入力装置として使用されている。

一方、CMOS イメージセンサは 1966 年にバイポーラ型のフォトトランジスタを使用したセンサに原型を見ることができる [2]。その後 1968 年に MOS 型のトランジスタを使用した発表がなされた [3]。その後しばらくして、1990 年に CMOS LSI のプロセスを用いたイメージセンサが発表された [4]。しかし、これは画素内部で増幅をする機能を持たないために (PPS, Passive Pixel Sensor) 画質が十分でなかった。現在主流の、画素内で増幅を行う (APS, Active Pixel Sensor) 方式は 1993 年に端を発するといわれている [5]。その後、様々な APS タイプのセンサーが開発されてきている。

CMOS イメージセンサは、センサの画素数と撮像速度が同等と仮定した場合に CCD イメージセンサに比べて低消費電力で構成が可能である。また、低電圧単一電源駆動可能、機能回路の組み込みができる等の様々な利点がある一方で、固定パターンノイズや熱に起因するランダムノイズ等の各種ノイズレベルが CCD に比べて高いために、CCD イメージセンサと一線を画しており、ノイズ特性の改善が求められていた。

固定パターンノイズと画素のリセットノイズは、相関2重サンプリング (CDS: correlated double sampling) という読み出し方式を、機能回路として CMOS イメージセンサに組み込むことでキャンセルができる。その一方で、CMOS イメージセンサの場合はその信号電荷の読み出し方式のため、多段に接続されたノイズ発生回路を通過して読み出されるため、ランダムノイズは CCD に比較して多く重畳する。

とはいうものの、理論的には CMOS イメージセンサがランダム雑音の点で CMOS イメージセンサよりも低レベルに抑制できる可能性については文献 [6] により議論されていた。これは CCD がノイズの帯域が画素周波数出決まるのに対し、CMOS では垂直転送周波数で決まるため有利なことに着目していた。

もう一つの問題は、標準プロセスで製造された CMOS イメージセンサは、その構造上の理由から、画素を 4Tr で構成した場合に完全転送が不可能であるために、残像が生ずる。これは高速撮像時に特に大きな問題となっていた。

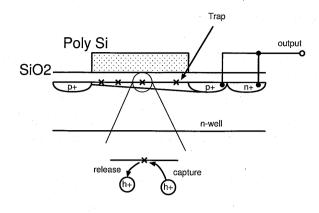

その問題解決として提案されたのが、画素部に埋め込みフォトダイオードと呼ばれる構造を使用することである [7,8]。もともと CCD に利用されていた技術であり、その名の通り表面付近の受光部にあたる PN 接合が、基板と同じ極性の不純物でドープされており、光電変換部が表面よりわずかに深いところにある。そのために、固体撮像素子で問題となる表面欠陥からノイズとして混入する暗電流を抑制できる。さらに、デバイスプロセスのチューニングにより受光した電荷の完全転送が可能となり、原理的に残像が残らない。このフォトダイオードの構造は、画素として構成する場合には必然的に 4Tr タイプとなるため、転送を行うことで画素内での信号増幅が可能であるのでセンサの高感度化を期待できる。これは、標準 CMOS のプロセスではなく、特殊なイメージセンサ専用プロセスとなる。

また利点として、CMOS イメージセンサは画素の読み出し自由度が高いことから画像圧縮 [9] や、非破壊読み出しによる動き検出 [10] のみならず、蓄積時間適応や時間積分広ダイナミックレンジ撮像等 [11] の高感度化にも非常に有効である。

広ダイナミックレンジイメージセンサは、一般的に高照度側のダイナミックレンジの拡大を主な目的とするもので、画素のトランジスタのサブスレッショルド領域を用いた Log 応答のイメージセンサ [12] を基本原理とするものや、高照度での飽和信号を時間的に多段階に分けて捨てる容量変調方式 [13] などがある。しかし、これら方式では撮像対象が高照度の場合に有効であり、低照度の場合には十分な S/N が得られないことが問題である。

一方、低照度側の S/N 改善のために、センサの感度を低照度に合わせてカラム増幅等で出力信号を増幅すると、カラム増幅以降の読み出し回路のランダムノイズは入力換算で増幅率だけ減少する。たとえば、カラムの増幅率を M 倍とすると、増幅回路以降のランダムノイズ成分が出力から見て 1/M に見える。しかし、信号も同時に M 倍されるために高照度時にセンサが飽和してしまうといった問題が生じる。これは例えばフルスケールの最大出力が FS(V) とすると増幅率が M 倍時に FS/M で飽和してしまう。これも十分な S/N が得られない。この一例として、画素、カラムFPN ノイズキャンセル回路とセンサ外部への読み出し回路を含めたトータルの系と

してのランダムノイズがどの様に発生するかを調べた報告がある [14] [15]。その結果、ランダムノイズの解析結果が CCD のランダムノイズよりも低減できる手法が提案され、実証されている [16]。この手法はフォトンカウントレベルの超低雑音読み出しを主眼としているため、カラム読み出し回路での増幅を行うがために前述の信号の飽和の問題があり、十分な S/N を得られないといった欠点があった。

以上のことから、低照度側のランダムノイズを抑制しつつ入力のダイナミックレンジも十分広い読み出し方式の開発が望まれる。低ノイズでかつダイナミックレンジの広い機能を持つイメージセンサが提案され、それが実証されれば、今までにない新しい CMOS イメージセンサを実現可能である。

# 1.2 本研究の目的

本研究の目的は、入力信号のダイナミックレンジを確保しつつランダムノイズを低 減することで、低照度側のダイナミックレンジを拡大する手法を検討することであ る。そのために、CMOSイメージセンサの機能回路の集積が可能であるという特徴 に注目し、以下の3種類の方式を研究した。第一に、画素信号が低レベル(低照度) 時には信号増幅をし、高レベル(高照度)時には信号増幅をせずにそのまま読み出 す、適応ゲインカラム増幅回路を組み込んだ CMOS イメージセンサを提案した。画 素信号からの出力信号を、各ピクセルごとに適応適に増幅することにより、SN の改 善と高照度時の飽和を抑制する。また、画素部に埋め込みフォトダイオード (Pinned Photo Diode) を用いることにより画素部からのノイズを低減する。さらに、画素回 路からの読み出しにブートストラップ機能を持たせて画素の出力信号を拡大した。こ れは読み出し制御信号の制御を工夫をすることで実現した。画素リセットを画素選 択よりも先に行い、アンオーバーラップさせることにより、画素選択をした時に、画 素の電圧検出部であるフローテイングデフュージョンがリセットレベルよりも電位的 に低い状態になる。このブートストラップ効果により画素信号の最大信号振幅を拡 大する。以上の技術を組み合わせ試作をした結果、イメージセンサの固定パターン ノイズが  $50\mu V_{rms}$ 、ランダムノイズが  $263\mu V_{rms}$  で SNR が CCD 相当である、71dBとなった。これは、発表当時で最も低いランダムノイズレベルを記録した。この研 究により、カラムで増幅することはランダムノイズの低減に非常に有効であること を確認した [17,18]。

第二に、2 重積分型カラム並列 A/D 変換器の量子化ノイズ低減効果について検討を行った。信号を多数回サンプル、A/D 変換をして、その平均を取ることでランダムノイズを低減する機能を持つ回路を提案した。単純に信号をN 倍高速に読み出し平均化を取ることでも実現できるが、回路が高速になるとノイズ帯域の増加につながるために効果が得られない。信号の平均化を考える場合、CMOS イメージセンサが出力する信号は毎回ほぼ同じ値を基準に、ランダムノイズの揺らぎが出力される

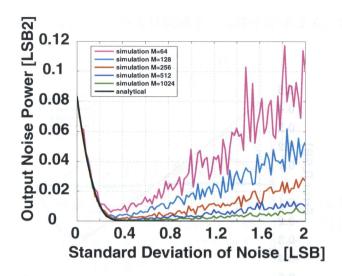

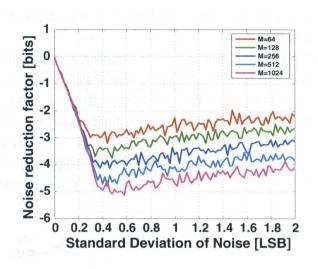

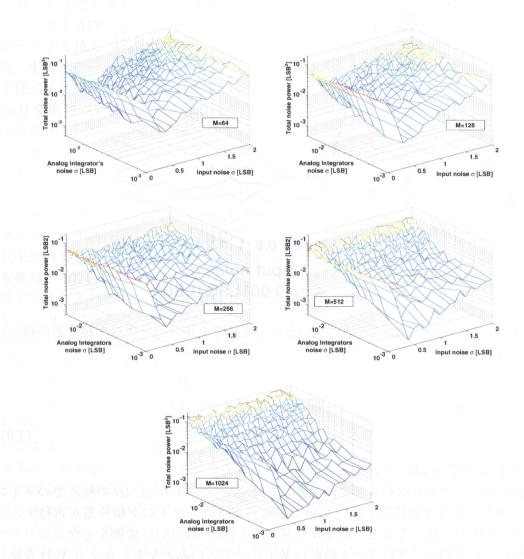

ので、ランダムノイズを効率的に低減するための回路的な工夫が必要となる。提案する2重積分型 A/D 変換器は、粗い A/D 変換を行ない入力信号のおおよその電圧値を推測するインクリメンタル A/D 変換 (ADC) モードと、センサのからのノイズの揺らぎを追従する信号追従・平均化モードをもつ。信号追従モードで出力される値はインクリメンタル ADC モードにおける出力値からの差分であり、1 クロックサイクルごとに 1 データを出力するために等価的に 1 クロックで A/D 変換を行なう。これは高速に A/D 変換をしていることと等価の効果を得ることが可能で、その信号平均化による演算で大幅な量子化ノイズとランダムノイズの低減効果が期待される。また、ノイズ低減効果は入力レンジのすべての範囲に適用でき、低照度のみならず高照度においてもノイズ低減効果を発揮する。特定の条件下において、熱ノイズと等価であるガウス分布に従う乱数を用いたシミュレーションにより、1024 回までの積分回数で約 5bit の改善効果が得られることを確認した。結果から、A/D 変換器の量子化ノイズがランダムノイズによって低減されることを確認した。インクリメンタル A/D 変換モードで 10bit の A/D 変換を行うとトータルで 15bit の高分解能カラム A/D 変換器が実現できる可能性を示唆した [20]。

第三に、適応積分機能共有型カラム並列巡回型 1.5bitA/D(analog-to-digital) 変換器について検討を行った。カラム回路に適応的に信号を積分する適応積分器を組み込む。適応積分器は演算に必要な単位容量 4つ、差動増幅器 1 つと比較器 1 つから構成され、入力信号をアナログ領域で 1 回から 16 回まで適応的に積分することでランダムノイズを入力換算で低減する。この適応積分器に追加の回路として 2 つ目の比較器を接続すると 1.5bit の A/D 変換器として動作が可能であることを見いだした。 1.5bit アーキテクチャは A/D 変換器によく用いられ、回路の必要精度を緩和することができる画期的な技術である [19]。このわずかな追加回路によって、カラムの限られた面積において高精度に A/D 変換を行うことが可能となり、原理的に広帯域のカラム以降のノイズが重畳しない構成を実現する。この方式は、カラムより面積の制限を受けやすい画素部で A/D 変換を行う方式 [21,22] に比べて面積的に余裕があるので、A/D 変換器の精度をとることが容易であり、画素それぞれに機能回路を組み込むことがないために高解像度化が容易に実現できる。

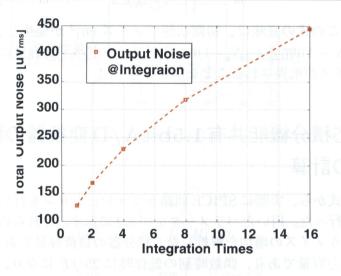

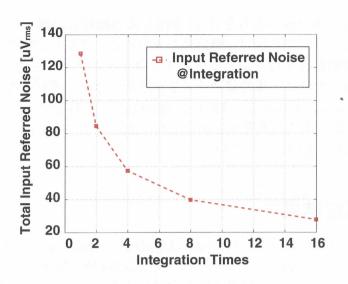

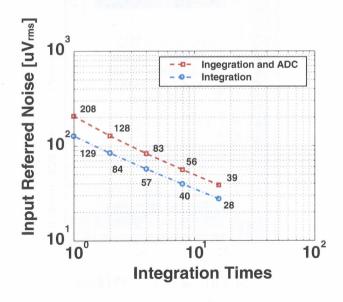

回路が積分器として動作する場合、熱に起因するランダムノイズを考慮したシミュレーションを行った結果、ランダムノイズの標準偏差が 16 回積分した場合に、入力換算で  $28\mu V_{rms}$  となり、適応ゲイン方式よりも高いノイズ低減効果を得られることが確認された。これは A/D 変換を行った場合の量子化ノイズ低減にも有効で、適応積分から A/D 変換を通したトータルのノイズとして  $32\mu V_{rms}$  程度のランダムノイズになる見通しを得た。また、回路が A/D 変換器として動作する場合のシミュレーションでは、回路にゲイン誤差、キャパシタミスマッチ、オフセットなどの特性を劣化させる要因が含まれていたとしても、補正なしで非線形性誤差が 1LSB 以下を実現できる結果を得て、非常に精度の高い A/D 変換器として動作することを確認した [23]。実際にイメージセンサの試作を行い測定を行った結果、暗時におけるランダムノイ

ズが入力換算で  $66.1 \mu V_{rms}$  まで低減でき、センサの出力が 0.9 V フルスケールを達成した。その結果ダイナミックレンジは 82.7 dB となり、広いダイナミックレンジかつ低ノイズの読み出し回路を実現した。

# 1.3 本論文の構成

本論文は以上に述べたように、CMOS イメージセンサの信号のダイナミックレンジを保ちつつ、ランダムノイズを低減する方法について、入力信号の大きさに応じて適応的に信号を増幅するカラム並列適応ゲイン方式、インクリメンタル A/D 変換器にノイズ低減モードを組み合わせて回路が発生するランダムノイズと量子化ノイズを低減するカラム並列 2 重積分型 A/D 変換方式、適応的に信号を積分することにより入力換算でノイズ低減を行いつつ高精度の A/D 変換を行うカラム並列適応積分機能共有 1.5bit 巡回型 A/D 変換器について研究したものであり、以下の構成をとる。

- 1章は緒言として、研究の背景、目的に関して述べた。

- 2章では高感度イメージセンサの基礎的考察として CMOS イメージセンサの基本動作ならびに雑音について述べる。

- 3章では適応ゲインカラム増幅に基づく CMOS イメージセンサについてノイズ解析、 実際に設計した回路、測定結果について述べる。

- 4章では2重積分型カラム並列 A/D 変換器についてのノイズ解析について述べる。 5章では適応積分機能共有型 1.5bit 巡回型 A/D 変換器についてノイズ解析、実際に 設計した回路、基本特性の測定結果について述べる。

- 6章で、結論として、本研究をまとめる。

# 参考文献

- [1] W. S. Boyle, G. E. Smith,"Charge Coupled Semiconductor Devices,"Bell Syst. Tech. J. pp.587-593, Apr. 1970

- [2] M. A. Schulster, G. Strull," A Monolithic Mosaic of Photon Sensors for Solid-State Imaging Applications," IEEE Trans. Electron Devices, vol.ED-13, No.12, pp.907-912, 1966

- [3] P.Noble,"Self-scanned silicon image detector arrays,"IEEE Trans. Electron Devices,vol.ED-15,pp.202-209,Apr.1968.

- [4] T. Miida," A 1.5MPixel Imager with Localized Hole-Modulation Method," in ISSCC Dig. Tech. Papers, 2002, pp.42-43

- [5] E. R. Fossum," Active Pixel Sensors: Are CCD's Dinosaurs?," in Proc. SPIE, vol.1900, pp.2-14, 1993

- [6] 松長、遠藤"CMOS イメージセンサのノイズキャンセル回路" 映像情報メディア学会報告書,vol.22,no.1,pp.7-11(Jan.,1998)

- [7] Paul P. K. Lee, et al.,"An Active Pixel Sensor Fabricated Using CMOS/CCD Process Technology", in Proc. IEEE Wordshop on CCDs and Advanced Image Sensors, 1995

- [8] R. M. Guidash et al.," A  $0.6\mu m$ CMOS pinned photodiode color imager technology," in IEDM Tech. Dig.,1997,p.927-129

- [9] S. Kawaito, et al.,"A Compressed Digital Output CMOS Image Sensor with Analog 2-D DCT Processors and DCT/Quantizer," in ISSCC Dig. Tech. Papers, 1997, pp.184-185

- [10] D. Handoko, et al." A CMOS Image sensor for focal-plane low-power motion vector estimation," Symp. VLSI Circuits Dig. 14, pp.28-29, June 2000

- [11] M. Mase, et al.," A 19.5b Dynamic Range CMOS Image Sensor with 12b Column-Parallel Cyclic A/D Converters," in ISSCC Dig. Tech. Papers, 2005, pp.350-351

- [12] Savvas G. Chamberlain, Jim P. Y. Lee,"A Novel Wide Dynamic Range Silicon Photodetector and Linear Imaging Array," IEEE Journal of Solid-State Circuits, vol. SC-19, no.1, pp. 41 48, Feb 1984.

- [13] S. Decker, R. McGrath, K. Brehmer, C. Soldini," A 256x256 CMOS Imaging Array with Wide Dynamic Range Pixels and Column-Parallel Digital Output," in ISSCC Dig. Tech. Papers, 1998, pp.176-177

- [14] N. Kawai, S. Kawahito, "Noise Analysis of High-Gain, Low-Noise Column Readout Circuits for CMOS Image Sensors," IEEE Trans. Electron Devices, vol.51, No.2, Feb. 2004. Solid-State Circuits, vol. 36, pp. 846 - 853, May 2001.

- [15] S. Kawahito, N.Kawai, "Noise calculatoin model for high-gain column amplifiers of CMOS image sensors," Proc. SPIE vol.5017 pp. 48-58, Jul 2003.

- [16] 河合信宏, "CMOS イメージセンサのノイズ解析と低ノイズ化に関する研究," 静岡大学博士論文, Feb. 2005

- [17] S. Kawahito, et al.," A Column-Based Pixel-Gain-Adaptive CMOS Image Sensor for Low-Light-Level Imaging," in ISSCC Dig. Tech. Papers, pp.224-225, 2003

- [18] M. Sakakibara, et al.," A High-Sensitivity CMOS Image Sensor With Gain-Adaptive Column Amplifiers," IEEE J. Solid-State Circuits, vol.40, No.5, May 2005

- [19] B. Ginetti, et al.," A CMOS 13-b Cyclic RSD A/D Converter," IEEE J. Solid-State Circuits, vol.27, No.7, Jul. 1992

- [20] M. Sakakibara, S. Kawahito," A Column Parallel Double Integration Type A/D Converter for CMOS Image Sensors," in ITC-CSCC Proc., vol.1, pp.189-190, 2005

- [21] D. X. D. Yang, A. El Gamal, B. Fowler, and H. Tian, "A 640 × 512 CMOS image sensor with ultra wide dynamic range floating-point pixel-level ADC," IEEE International Solid-State Circuits Conference, vol. XLII, pp. 308 309, February 1999

- [22] L. G. McIlrath, "A low-power low-noise ultrawide-dynamic-range CMOS imager with pixel-parallel A/D conversion," IEEE Journal of Solid-State Circuits, vol. 36, pp. 846 853, May 2001

- [23] M. Skakibara, S. Kawahito,"Column Parallel Low Noise Digital Redout Circuits Using Adaptive Integration for CMOS Image Sensors," Proc. of The 2nd International Symposium on Nanovision Science 5-19, pp93-94, Oct. 2005

# 第2章

# 低ノイズイメージセンサの基礎的考察

# 2.1 はじめに

本章では、CMOSイメージセンサによる低ノイズイメージセンサの基礎的考察として、一般的な CMOSイメージセンサの構成と、回路で発生する各種ノイズについて述べる。さらに、熱に起因するランダムの解析方法についても簡単に触れる。

CMOS イメージセンサは、受光部、画素信号読み出し回路、カラム信号読み出し 回路と外部読み出しのためのバッファの4つの回路から構成される。これら各部分は いろいろな構成手法があり、その構成それぞれで発生するノイズが異なる。また、回 路の動作手順により、スイッチーつ切る順番次第でノイズの出力のされ方が異なる。

CMOS イメージセンサで低ノイズ読み出しを実現するために、信号が読み出されるまでの全体の系としてのノイズがどの程度になるのかを解析によりあらかじめ見積もることが重要になる。

以下に、CMOSイメージセンサの撮像の基本動作とその回路構成について述べる。

# 2.2 CMOS イメージセンサによる撮像

# 2.2.1 撮像の基本動作

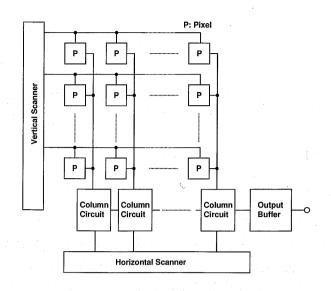

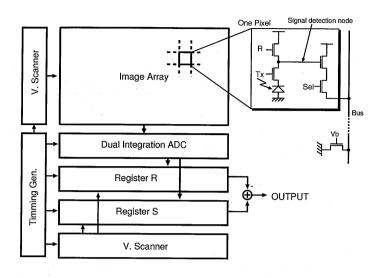

図 2.1 に CMOS イメージセンサの基本構成を示す。CMOS イメージセンサによる 撮像は、画素より信号を垂直選択信号により並列にカラムへの読み出し回路へ出力 し、カラム読み出し回路に信号を記憶・演算した後に水平選択信号により順次走査 をして外部に出力をする構成を取る。

各々の構成部位は、CMOSイメージセンサの設計自由度の高さからいろいろな方式が提案されている。以下に、CMOSイメージセンサで一般的に用いられている各部の構成を述べる。

## 2.2.2 光電変換部

銀塩カメラの受光部はフィルムの銀化合物であるが、これと対になる CMOS イメージセンサの受光部はフォトダイオードである。これは CMOS イメージセンサに限らず、CCD イメージセンサも同様である。

図 2.1: CMOS イメージセンサの基本構成

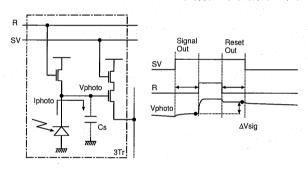

3Tr 方式と呼ばれる CMOS イメージセンサの画素の回路図を図 2.2 に示す。フォト

図 2.2: 3Tr 方式

ダイオードに入射した光は、光起電力効果によって電子、正孔対が生成され接合部 に拡散、もしくは空乏層で発生した電子はn側へ、正孔はp側へ移動する。この結 果、p側は正に、n側は負に帯電し、外部に起電力を示す。この電圧はこのフォトダ イオードの寄生容量を $C_s$ とすると、発生する光電流を $I_{photo}$ 蓄積時間(露光時間)を Tとして

$$V_{photo} = \frac{\int_0^T I_{photo}(t)dt}{C_s}$$

で表される。蓄積時間中の光電流  $I_{photo}(t)$  が一定であるならば、

$$(2.1)$$

$$V_{photo} = \frac{T \cdot I_{photo}}{C_s} = \frac{Q_{photo}}{C_s} \tag{2.2}$$

となる。寄生容量 $C_s$ は小さいほど同じ光量に対し電圧感度が高い。例えば、フォト ダイオードの寄生容量  $C_s$  を 2fF と見積もると電子 1 つで約  $80\mu V$  の出力が得られ

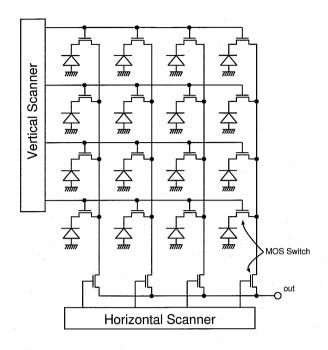

図 2.3: パッシブピクセルセンサ

る。この値は変換ゲインと呼ばれイメージセンサの性能を示す重要なパラメータの 一つである。

フォトダイオードで電圧値となった光信号を、電圧検出トランジスタでソースフォロワによりバッファして読み出し、カラム回路に信号を送る。一定時間露光した後は、画素部をリセットトランジスタにより受光で生じた光信号である電荷をリセットして初期化する。出力回路は受光して出力された信号と、リセットして出力された信号の差をとることにより相関2重サンプリング(CDS)を行い画素部の閾値ばらつき等をキャンセルする。

## 2.2.3 パッシブピクセルセンサ

MOS型イメージセンサ [1], [2] が考案された当時は、図 2.3 に示すように画素からの信号を直接カラム回路に読み出していた。これはダイナミックランダムアクセスメモリ (DRAM) のアレイとほぼ同じ構造である。受光により蓄積した信号を垂直スキャナで選択し、カラムの水平スキャナで順次走査をし信号を読み出す。これは固定パターンが多いことや出力段の配線容量により感度が低下すると言った問題があったが、後述のアクティブピクセルセンサの発明 [4]、開発 [5] [6] [7] により、感度、固定パターン雑音等の大幅な改善が可能となった。このアクティブピクセルセンサは MOS型イメージセンサの流れを汲むものであるが、現在の集積回路技術の主流である CMOS 技術で実現されて [3]、一般に CMOS イメージセンサと呼ばれる。

前述3Tr方式はパッシブピクセルセンサではなくアクティブピクセルセンサに属する。

### 2.2.4 アクティブピクセルセンサ

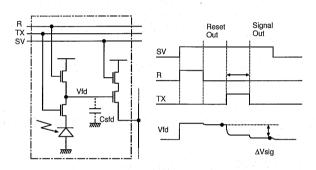

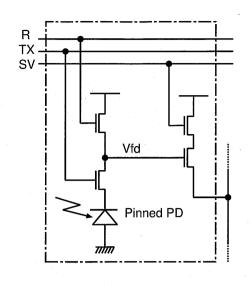

パッシブピクセルセンサ(PPS)と比較して、アクティブピクセルセンサは画素内で信号を増幅する回路を持たせてカラムに出力する。 $3\mathrm{Tr}$  方式では図 2.3 ソースフォロワトランジスタが増幅器になっており、バッファ機能を持たせてある。ソースフォロワの増幅率は、トランジスタの基板効果の影響を無視すると約 1 倍である。 $3\mathrm{Tr}$  方式では一般的に、受光面積を大きくとると光電流  $I_{photo}$  が増すが、画素の寄生容量  $C_s$  も増すので、検出電圧が大きくなることはない。この問題解決に、画素内に増幅率 1 倍以上の増幅器を持たせた  $4\mathrm{Tr}$  方式が考案された [8]。図 2.4 に  $4\mathrm{Tr}$  方式のピクセル部を示す。これは、受光部の面積を増やして光電流を増やすと、寄生容量まで増え

図 2.4: 4Tr 方式

て感度がとれない欠点を克服した回路でもある。4Tr 方式の動作は、ターゲットのピクセルが SV で信号選択され、その後リセット R により、フローティングデフュージョン  $V_{fd}$  をリセットする。その信号をカラムに読み出し記憶する。その後、トランスファゲート Tx を ON して信号を転送する。もし、受光した光電流がロスなくフローティングデフュージョン側に転送されるとすると、

$$V_{fd} = \frac{Q_{photo}}{C_{sfd}} = \frac{V_{photo} \cdot C_s}{C_{sfd}}$$

(2.3)

となり、フローティングデフュージョンの寄生容量と受光部の寄生容量の比 $C_s/C_{sfd}$ で信号電圧が変化する。これはフローティングデフュージョンの寄生容量が受光部の寄生容量よりも小さい場合に画素内で増幅されることを意味する。また、この読み出し方式はリセットレベルが先に出力されるため、後段のCDS 回路において閾値ばらつきによる固定パターンノイズとともに、浮遊容量 $C_{sfd}$  に蓄積されたリセットノイズをキャンセルできる優れた特徴をもつ。

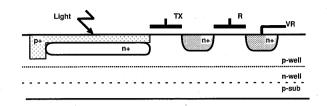

図 2.5: 画素部:埋め込みフォトダイオード

## 2.2.5 埋め込みフォトダイオードと完全転送

前述の4Tr 方式により、固定パターンノイズ、リセットノイズ、感度の問題を解決できることを述べた。これら以外に、センサの特性を決定する重要なパラメータとして暗電流がある。画素に使用されるフォトダイオードは pn 接合で作成されるために、原理的に光が当たらない状態でもわずかに電流が流れる。この接合の空乏層が $Si-Si_2$ 界面に接していると界面の欠陥からさらに多くの電流が発生して暗電流の増加につながる。この暗電流の増加を防ぐのが、埋め込みフォトダイオード構造である。埋め込みフォトダイオードは図2.5に示すように、受光部の表面部を基板と同じタイプの不純物で覆ったもので、受光部である pn 接合が $Si-Si_2$ 界面に接しておらず暗電流の抑制に非常に効果的である。

もう一つの重要な技術として受光部から信号電荷の完全転送があげられる。標準 CMOS プロセスで製造されたイメージセンサでは受光部からフローティングデフュージョンに転送される電荷は完全転送されない。これは、トランスファゲートを開いた直後は、電荷が主にドリフトで流れるのに対し、転送終了直前の電荷は受光部に光電変換された電荷がほとんどなく、ほぼ拡散によってしかフローティングディフュージョン側に流れないため残電荷が生ずることによって起こる。この残電荷の量は受光量と TX ゲートを解放している時間の逆数に比例し、次のフレームに残像として読み出され、高速撮像時に特に問題となる。これらは、ゲートと受光部と転送部のデバイス構造と、そのポテンシャルプロファイルをチューニングし、受光部に電荷が残らない完全転送を行うことで解決している。

埋め込みフォトダイオードとその完全転送のためのデバイス構造のチューニング は標準の CMOS プロセスでは不可能であるので、イメージセンサ専用プロセスを必要とする。

## 2.2.6 カラムノイズキャンセル回路

カラムの読み出し回路について説明する。現在の CMOS イメージセンサは、カラムの読み出し回路に固定パターンノイズのキャンセル機能を持たせている。

前述の画素構造を見ると、現在主流になっている 4Tr 方式(埋め込み型を含む)や一部で使用されている 3Tr 方式はどれも画素内にソースフォロワのアンプを持たせ

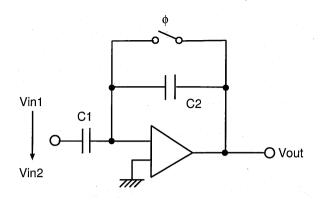

図 2.6: カラム読み出し回路: カラムノイズキャンセル回路

たものである。理想的には、どの画素であろうと同じ特性でソースフォロワの入力信号が出力に現れる。しかしながら、実際のCMOSイメージセンサには製造上のプロセスばらつきが存在する。そのばらつきは、主にソースフォロワを構成するアンプの閾値ばらつきとなってCMOSイメージセンサの信号を劣化させる。これは、例えばソースフォロワの入力電圧(フォトダイオードの出力電圧)がすべての画素で同じであった場合であっても、閾値ばらつきの影響を受けて各画素ごとに違った電圧値を出力する。注意することは、各画素ごとに出力電圧はばらつくが、そのばらつき値が固定であり、読み出すたびに毎回同じばらつき値を出力するとこである。このような特徴からこの閾値ばらつきは後述するFPN(fixed pattern noise)と呼ばれる。

この閾値ばらつきによるノイズを、カラムのノイズキャンセル回路は除去することが可能である。この回路図を図 2.6 に示す。スイッチ、キャパシタ 2 つとアンプから構成され、スイッチトキャパシタ回路の構成をとる。この回路の動作を順を追って説明する。まず、入力側に  $V_{in1}$  が入力される。この時スイッチ $\phi$ は ON したままでフィードバック側の入出力は短絡されている。入力側の容量  $C_1$  に蓄積される信号電荷は

$$Q = C_1 \cdot V_{in1}$$

と示される。続いてスイッチ $\phi$ がOFFした後、入力信号が $V_{in2}$ に変化する。この時 $C_1,C_2$ に蓄積された信号電荷の総量は電荷保存則から変化しないので、

$$Q = C_1 \cdot V_{in2} + C_2 \cdot V_{out}$$

となる。結果として出力される電圧は

$$V_{out} = \frac{C_1}{C_2} (V_{in1} - V_{in2})$$

となる。ここでキャパシタの容量値が $C_1 = C_2$ とすると

$$V_{out} = V_{in1} - V_{in2}$$

となる。結果を見ると、時間的に変化する入力信号の差分を出力しているのみであるが、これが非常に重要な意味を持つ。

ここで 3Tr の場合、まず信号レベル  $(V_{sig})$  を画素から読み出し、続いて画素をリセットしそのリセットレベルを同じソースフォロワを通して読み出す  $(V'_{reset})$ 。各々の信号に閾値ばらつき  $(V_{offset})$  がある場合

$$V_{out} = (V_{sig} + V_{offset}) - (V'_{reset} + V_{offset})$$

(2.4)

$$= V_{sig} - V'_{reset} \tag{2.5}$$

とオフセットによらないリセットレベルと信号レベルの差分が出力されることがわかる。3Tr の場合は特殊な構成にしない限り、信号レベルが先に出力され、リセット信号が後で出力されるために、画素のリセット時に信号と相関のないリセットのノイズが重畳される。これは、リセットレベルを信号レベルより先に出力すると、必然的にそれまで蓄積した信号電荷をリセット動作で初期化するためである。

一方、4Tr の場合は信号検出部が受光部とトランスファーゲートで分離されているために、先に信号検出部をリセットすることが可能である。そのため、リセットレベル  $(V_{reset})$  を先に読み、その後信号レベル  $(V_{sig})$  を読み出すことが可能である。出力信号は

$$V_{out} = (V_{reset} + V_{offset}) - (V_{sig} - V_{offset})$$

(2.6)

$$= V_{reset} - V_{sig} \tag{2.7}$$

となる。4Tr の場合も同様に、信号検出部をリセットするとリセットノイズが重畳するが、信号レベルはリセットノイズの重畳したリセットレベルを基準に出力されるために、両者にの差分を取ることで画素の閾値ばらつきのみでなく画素のリセットノイズを除去することが可能である。

この技術は CDS(correlated double sampling: 相関 2 重サンプリング) と呼ばれ CMOS イメージセンサに欠かせないノイズキャンセル手法である。3Tr の場合の CDS は通常固定パターンノイズ (FPN) のみの除去に有効であるが、4Tr の場合の CDS は FPN と画素のリセットノイズの両者に対して有効である。

# 2.2.7 A/D 変換器

CMOS イメージセンサは、その特徴である回路集積の自由度から A/D 変換器を内部に組み込むことが可能である。

CMOS イメージセンサで使用される A/D 変換器は大きく分けて 3 つある。画素内部で A/D 変換を行うもの [10] [11]、カラムで A/D 変換を行うもの [12]- [13] と最終読み出し部で A/D 変換器を行うものがある。それぞれの方式で、一長一短がある。

後に詳細を述べるが、回路の支配的なノイズに熱ノイズがある。この雑音電力の 大きさは、ノイズを発生する回路の帯域に比例する。この理由により、最終読み出

し部で A/D 変換を行うと、その帯域の広さから多くのランダムノイズ (熱ノイズ) が 信号に重畳する。従って最終読み出し部で A/D 変換を行う方式は、原理的に帯域の 広いノイズが必ず重畳するので低ノイズ読み出し回路には向かない。

画素内に信号処理回路を設けて狭い帯域、ピクセルレベルで A/D 変換をする方 式 [10] [11] は画素内に比較器などの回路を集積することから、省面積化には不向き である。さらに、画素のバラツキやADCの分解能不足により特性の劣化が顕著であ る。一方、カラムに A/D 変換器を設けるとノイズ帯域が狭い状態で A/D 変換を行 うことができ、量子化された後は原理的にノイズが重畳せず非常に有効である. し かしながら、近年報告されているカラムに A/D 変換器を搭載しているイメージセン サ [12]- [13] の分解能は 10bit から 11bit であり、十分なデジタルダイナミックレンジ が得られていない。また、12bit の分解能を [14] が報告しているが、このセンサの実 質的な精度は 10bit 程度である。初めてカラム A/D 変換器で 12bit の精度を達成した のは文献 [15] であろう。カラム A/D 変換器の高精度化が困難な理由は、画素単位で A/D変換する方式に比べれば面積に余裕があるものの、依然としてカラム回路の横 方向の幅は画素のサイズで制限されるため、使用できるトランジスタやキャパシタ のサイズが制限され、高精度化、低ノイズ化が難しいためである。とはいえ、これ らの問題が解決された場合、カラムでの並列 A/D 変換が最も有効であるといえる。 後の章で述べる適応積分機能共有カラム巡回型 A/D 変換器と2 重積分型カラム A/D 変換器は、ノイズ帯域の狭いカラムで信号処理を行ないつつ A/D 変換を行うこ

とでランダムノイズを低減する全く新しい方式である。本研究では、14bitから15bit の分解能を目標とする。

#### CMOSイメージセンサのノイズ 2.3

本手法は、信号レベルの低い低照度側のダイナミックレンジを拡大することに主眼 を置いている。この低照度側のダイナミックレンジは、いわゆるノイズと呼ばれる受 光部で発生した信号電荷(電圧)以外の不要な信号が信号読み出し回路で発生するた めに、低照度条件下での出力信号値が制限されることで決定される。ここで、CMOS イメージセンサのノイズについて述べる。ノイズは以下の

- 固定パターンノイズ

- 熱ノイズ

- 1/fノイズ

- リセットノイズ

- ショットノイズ

- 量子化ノイズ

#### その他のノイズ

に大別され、一般的には、固定パターン以外のノイズをまとめて、ランダムノイズ という。

本研究では、この抵抗体やトランジスタが存在すると必然的に発生する熱ノイズをいかに低減するかを目的としている。以降、3,4,5章において特に断りがない限り、ランダムノイズとは熱に起因する熱ノイズのことのみをさす。

以下各々について述べる。

## 2.3.1 固定パターンノイズ

固定パターンノイズとは読み出すごとによって毎回変らない一定のノイズのことである。

CMOS イメージセンサは、非常に微細なプロセスである LSI の技術で製造されるので、トランジスタにガウス分布に従う特性のばらつきが生じる。具体的にはトランジスタの閾値ばらつき、トランジスタのサイズばらつき、受光部の感度ばらつき、開口率ばらつき、暗電流ばらつき、アンプのゲインばらつき(キャパシタミスマッチ)等が含まれる。

一般にイメージセンサで問題となるのは、画素の閾値ばらつきと読み出し回路の閾値ばらつきである。固定パターンノイズについては信号を読み出したときに毎回一定であることから閾値ばらつきは CDS(correlated double sampling) 技術により除去可能である。また、デジタル領域でもアナログ回路と同じように、リセットレベルのデジタル値と信号レベルのデジタル値の差分を取ることで CDS も可能である。この場合、固定パターンノイズの除去精度は演算におけるデジタル値のダイナミックレンジ (分解能) に依存することになる。キャパシタミスマッチや開口率ばらつきを補正する場合はデジタル領域で行われるが、これらの精度もデジタル値のダイナミックレンジ (分解能) に依存することになる。

## 2.3.2 熱ノイズ

熱ノイズは抵抗体が存在するところに発生するノイズである。

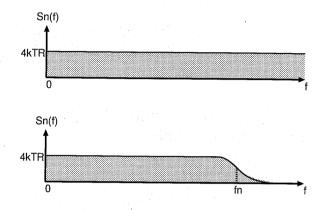

抵抗体は内部の原子が熱エネルギーによって振動し、自由電子と衝突を繰り返す結果、電子が不規則に運動し、電圧ゆらぎを生じる. 熱ノイズはジョンソンノイズあるいは、ホワイトノイズとも呼ばれる。ナイキストは熱ノイズの解析に熱力学的な理論を導入して、抵抗体の発生するノイズ電力を導いた。これを回路上、最大電力を取り出す条件で導きだすと、次式の電圧2乗平均ノイズ

$$\overline{v_n^2} = 4kTR\Delta f \tag{2.8}$$

が得られる。ここで。 $k=1.38\times 10^{-23}J/K$  はボルツマン定数、T は絶対温度、 R は抵抗体の抵抗値、 $\Delta f$  は、対象とする周波数帯域幅である。これは、ノイズ電力スペクトルが、 $S_n(f)=\overline{v_n^2}/\Delta f=4kTR$  と一定になることを意味し、ホワイトノイズと言われるゆえんである。なお、雑音電力スペクトルとしては、周波数を負の領域まで考えた両側周波数表示の場合には、 $S_n(f)=\overline{v_n^2}/\Delta f=2kTR$  となる。CMOS イメージセンサでは、トランジスタが CMOS スイッチとして線形領域で動作する場合そのスイッチの ON 抵抗がノイズ源になる。また、トランジスタがアンプとして動作する飽和領域ではアンプの相互コンダクタンス  $g_m$  がノイズスペクトルに影響する。この場合のノイズスペクトルは

$$\overline{v_n^2} = 4 \cdot \gamma k T \frac{1}{q_m} \Delta f \tag{2.9}$$

となる。ここでの係数  $\gamma$  は基板バイアスの係数とは異なるもので、長チャネルデバイスで 2/3 の値をとる。サブミクロンデバイスではこの値より少し大きめになるといわれている [16]。

# 2.3.3 1/fノイズ

1/f ノイズとは主に、FET トランジスタのゲート酸化膜-基板間の界面で発生する ノイズであるといわれており、二通りの考え方がある。[16] [17]

トランジスタが ON(飽和領域、線形領域)している状態では、基板の極性が反転し少数キャリアが増す。この過剰少数キャリアのうち、表面近く、ゲート側を流れるキャリアが CMOS の製造工程で生じた、絶縁膜である二酸化シリコンと基板との界面の欠陥準位にトラップされる。また、そのトラップされたキャリアが一定時間後にランダムなタイミングで放出される。ある考え方では、このキャリアが  $SiO_2-Si$  界面で格子振動を引き起こし移動度の変調を引き起こす結果生じるといわれている。このノイズはトランジスタのゲート長 L、ゲート幅 W、酸化膜厚間容量 C とすると

$$\overline{v_n^2} = \frac{K_1}{C_{cr}WL} \cdot \frac{\Delta f}{f} \tag{2.10}$$

と記述される。もう一方の考え方では、この放出された少数キャリアがチャネルの 電荷量を変化させてノイズとなる。ノイズ電力を示す式では

$$\overline{v_n^2} = \frac{K_f}{C_{ox}^2 WL} \cdot \frac{\Delta f}{f^c} \tag{2.11}$$

となり、周波数の逆数に比例し、係数 c は n 型デバイスで 0.7-1.2 の値をとるといわれる。

この係数  $K_f$  はフリッカ雑音係数で

$$K_{fn} = 5 \times 10^{-31} \ (V/cm^2) \ (NMOS)$$

(2.12)

$$K_{fp} = 2 \times 10^{-32} \, (V/cm^2) \quad (PMOS)$$

(2.13)

でプロセスによらずほぼ一定といわれるている [16]。

このままであると、直流付近のノイズが無限大まで増えてしまう。イメージセンサの 1/f ノイズは文献 [18]、[19]、[20] によると回路のカットオフ時定数を  $\tau_0$ 、サンプリング 時間差を  $t_0$  として、 $\lambda=\frac{t_0}{\tau_0}$ 。また、1/f ノイズのスペクトル密度関数  $N_f(f)=N_{f1}/|f|$  として相関 2 重サンプリング回路に適用させると以下の式 2.14

$$\overline{v_n^2} = 4K_{f1}(0.577 + \ln \lambda) \quad for \quad \lambda > 3$$

(2.14)

で記述できる。このノイズは、スイッチトキャパシタ回路を適用した式であり今回の設計に使う適応ゲインカラム増幅器もスイッチトキャパシタ回路であるので、フリッカ雑音係数がわかればこれを適用可能である。注意することは、本論文で解析しているランダムノイズは 1/f ノイズを含んでいない。これは使用するプロセスでの 1/f の係数が不明であることと、提案方式では 1/f ノイズが支配的ではない、高い周波数で回路が動作するためである。

### 2.3.4 リセットノイズ

リセットノイズとは、ある電圧ノードを CMOS スイッチによってバイアスしていたとき、そのスイッチを切るときに発生するノイズである。したがって、CMOS スイッチがあるところには必ず発生する。リセットノイズとして主なものは、チャージインジェクション、フィードスルーとスイッチで発生する熱ノイズである。

チャージインジェクションとはトランジスタのチャネル領域での電荷がスイッチを切られた瞬間に、バイアスされていた側に漏れるキャリア電荷によってバイアス電圧が変動してしまうことによるノイズである。

フィードスルーはスイッチの電圧が ON から OFF(一般的には VDD から OV に変化)になった瞬間にゲートとそのノード間の寄生容量と、ノードと基板間の寄生容量によって分圧されることによってノードの電圧が変化することによるものである。なお、両者の区別をせずに上記 2 つを合わせて、単にインジェクションと言うこともある。スイッチで発生する熱ノイズはスイッチが切れた瞬間の電圧をサンプルする。熱ノイズはランダムに揺らいでいるがスイッチをきった瞬間にリセットノイズとして固定の電圧値に定まる。

CMOS イメージセンサでリセットノイズと呼ばれるものは、一般に画素で生ずるリセットノイズのことを示す。リセットノイズは、もともとランダムであるが、スイッチを切った後にそのノイズが固定することで固定パターンのノイズと同じ振る舞いをするので、4Trの画素で構成されるものについては CDS 動作で除去が可能である。

## 2.3.5 ショットノイズ

ショットノイズには2種類のものがある。一つは光ショットノイズであり、もう一つは暗電流ショットノイズである。光ショットノイズとはセンサの受光部が光電変換した際に発生するノイズである。ショットノイズの電力は熱ノイズと同様に光の強さ、すなわち光度に比例し、受光すれば原理的に発生する。

受光した際に発生する電荷量を N 個とすると、ランダム的に  $\sqrt{N}$  の電荷が発生する。

同様に、暗電流ショットノイズもその暗電流の電荷量  $N_d$  に対してランダム的に  $\sqrt{N_d}$  の電荷が発生する。これらのショットノイズは、検出部であるフォトダイオードで必ず発生する低減できないノイズである。

## 2.3.6 量子化ノイズ

量子化ノイズとは連続信号であるアナログ信号を、離散信号であるデジタル信号 に変換するときに発生するノイズである。

Nbit 分解能の A/D 変換器が変換できる最小信号は、電圧のフルスケールを FS として、

$$1LSB = \frac{FS}{2^N} \tag{2.15}$$

である。この 1LSB より低い信号については 1bit の判定ができず誤差成分となる。長時間にわたり、AD 変換を行った場合この 1LSB 以下の信号はランダムに出現し、結果としてこの範囲の電圧は一様な確率密度で分布する。

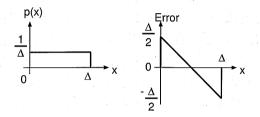

一般に量子化ステップ 1LSB を q とおけば、量子化誤差 (e) の分布密度は 1/q で一様となる。この雑音の 2 乗平均誤差  $\overline{e^2}$  を求めると以下の式 2.16 となる。

$$\overline{e^2} = \int_{\frac{1}{2}}^{\frac{1}{2}} e^2 p(e) = \frac{q^2}{12}$$

(2.16)

# 2.3.7 その他のノイズ

前述以外のノイズをその他のノイズとする。前述までのノイズは回路自体が発生するノイズであるので別名真性ノイズとも言われる。一方、各々の回路を組み合わせたとき問題となるノイズがあり、環境ノイズ(外来ノイズ)とも言われる。これは、システムとして回路を組んだときに問題となるノイズである。一例としてはデジタル回路からアナログ回路の電源線、グランド線等へ混入するノイズや、アンテナからの放射ノイズ等がある。集積回路を設計する場合は、周りの回路からのノイズの感度を高くしないことと、自分自身がノイズ発生源とならない、差動構成などの回路にするなどの対策が必要がある。

これらの対策には、機能回路を実現する際に採用するアーキテクチャの考慮以外にレイアウトの工夫が必要である。例を挙げるとデジタルの信号線とアナログの信号線は平行にしない、スイッチの拡散層は遮光する、アンプの入力への配線は極力短くする、キャパシタのトップメタル(基板から遠い側)を低ノイズにしたい側に使用する、基板とのコンタクトを十分にとりインピーダンスを十分下げるなどである。

# 参考文献

- [1] G.P.Weckler,"Integrated arrays of silicon photodetectors for image sensing,"IEEE J.Solid-State Circuits,vol.SC-2,pp.65-73,1967.

- [2] R.Dyck and G.P.Weckler,"Integrated arrays of silicon photodetectors for image sensing,"IEEE Trans.Electron Devices,vol.ED-15,pp.196-201,Apr.1968

- [3] E. R. Fossum," Active Pixel Sensors: Are CCD's Dinosaurs?," in Proc. SPIE, vol.1900, pp.2-14, 1993

- [4] P.Noble, "Self-scanned silicon image detector arrays," IEEE Trans. Electron Devices, vol. ED-15, pp. 202-209, Apr. 1968.

- [5] F. Andoh, K. Taketosi, J. Yamazaki, M. Sugawara, Y. Fujita, K. Mitani, Y. Matuzawa, K. Miyata, and S. Araki, "A 250 000 pixel image sensor with FET amplification at each pixel for high-speed television cameras," in ISSCC Dig. Tech. Papers, 1990, pp. 212-213.

- [6] H. Kawasima, F. Andoh, N. Nurata, K. Tanaka, M. Yamawaki, and K. Taketosi, "A 1/4 inch format 250 000 pixel amplifier MOS image sensor using CMOS process," in IEEE IEDM Tech Dig., 1993, pp. 575-578.

- [7] F.Andoh, K.Taketosi, J. Yamazaki, MSugawara, Y. Fujita, K. Mitani, Y. Matuzawa, K. Miyata, and S. Araki, "An amplified Mos Imager suited for image processing," in ISSCC Dig. Tech. Papers, 1994, pp. 228-229.

- [8] M.Kyomasu,"New CMOS Imager Using Photodiode as Current Source,"IEEE J.Solid-State Circuits,vol.26,pp.1116-1122,Aug.1991.

- [9] K.Yonemoto, H.Sumi," A CMOS Image Sensor with a Simple Fixed-Pattern-Noise-Reduction Technology and a Hole Accumulation Diode," IEEE J.Solid-State Circuits, vol. 35, No. 12, pp. 2038-2043, Dec. 2000.

- [10] D. X. D. Yang, A. El Gamal, B. Fowler, and H. Tian, "A 640 × 512 CMOS image sen sor with ultra wide dynamic range floating-point pixel-level ADC," IEEE Intern ational Solid-State Circuits Conference, vol. XLII, pp. 308 309, February 19 99.

- [11] L. G. McIlrath, "A low-power low-noise ultrawide-dynamic-range CMOS imager wit h pixel-parallel A/D conversion," IEEE Journal of Solid-State Circuits, vol. 3 6, pp. 846 - 853, May 2001.

- [12] I. Takayanagi, M. Shirakawa, K. Mitani, M. Sugawara, S. Iversen, J. Moholt, J. Nakamura, and E. R. Fossum, "A 1 1/4 inch 8.3M pixel digital output CMOS APS for UDTV application," IEEE International Solid-State Circuits Conference, vol. XLVI, pp. 216 217, February 2003.

- [13] K. Findlater, R. Henderson, D. Baxter, J. E. D. Hurwitz, L. Grant, Y. Cazaux, F. Roy, D. Herault, and Y. Marcellier, "SXGA Pinned photodiode CMOS image sensor in 0.35 μ m technology," IEEE International Solid-State Circuits Conference, vol. XLVI, pp. 218 - 219, February 2003.

- [14] J. Nakamura, B.Pain, T. Nomoto, T. Nakamura, and E. R. Fossum, "On-focal-plane sigmal processing for current-mode active pixel sensors," IEEE Trans. Electron devices, Vol. 44, No. 10, pp. 1747-1758, Octover, 1997.

- [15] M. Mase, et al.,"A 19.5b Dynamic Range CMOS Image Sensor with 12b COlumn-Parallel Cyclic A/D Converters," in ISSCC Dig. Tech. Papers, 2005, pp.350-351

- [16] B. Razavi," Design of Analog CMOS Integrated Circuits," McGraw-Hill, 2001

- [17] Y. Tsividis,"Operation and Modeling of The MOS Transistor," Second Ed.,McGraw-Hill, 1999

- [18] H.M.Wey and W.Guggenbuhl,"An Improved Correlated Double Sampling Circuit for Low Noise Charge-Coupled Devices,"IEEE Trans., vol.37,no.12,Dec. 1990

- [19] R.J.Kansy,"Response of a correlated double sampling circuit to 1/f noise,"IEEE J. Solid-State Circuits, vol.SC-15,pp.373-375, June 1980.

- [20] G.R.Hopkinson and D.H.Lumb,"Noise reduction techniques for CCD image sensors," J.Phys.E:Sci.Instrum.,vol.15,pp.1214-1222,1982.

# 第3章

# 適応ゲインカラム増幅に基づく高感度 CMOSイメージセンサ

## 3.1 はじめに

本章では低照度側のダイナミックレンジの拡大手法の一つとして、適応ゲインカラム増幅器を用いた高感度 CMOS イメージセンサの研究について述べる。適応ゲインカラム増幅器は、他の章の方式よりも回路構成がシンプルであり、シングルエンドのアンプを使用しているために、カラムの狭い面積を有効に活用しつつ、大幅なノイズ低減を可能とする。

イメージセンサのダイナミックレンジは、センサからの出力が飽和しない最大値を取る高照度での出力信号と、光の照射がない暗時での読み出し回路の系を通した全体のノイズレベルとの比(S/N, signal-to-noise ratio)で決まる。CMOSイメージセンサがエリアセンサタイプでアナログ出力の構成を取る場合、原理的に読み出しの系で発生するノイズがCCDに比べて高い。

これは、信号が回路を通過するときに重畳するノイズは、回路の帯域幅に比例するためである。CCDイメージセンサの場合は、CCDそれ自体は非常に低雑音であり、現在はほぼ無雑音で信号電荷をセンサの最終読み出し部までバケツリレー方式の転送により読み出すことができる。唯一のノイズ源は電荷を電圧に変換し、それをソースフォロワでセンサの外部に出力するバッファである。このバッファの帯域はピクセルレートとほぼ同等であるので大きなノイズが重畳する。

一方、CMOSイメージセンサの場合は画素部で信号電荷を電圧値に変換し、ソースフォロワのバッファを介してカラムの読み出し回路に出力する。このソースフォロワとカラム読み出し回路でノイズが重畳するが、これら回路はカラム並列に動作するために動作はさほど速くない。つまり、帯域が狭いので重畳するランダムノイズも小さい。最後に、カラム読み出し回路にホールドされた信号を水平スキャン信号により最終的な出力バッファを介して外部に出力する。このバッファの帯域はピクセルレートとほぼ同等である。以上のことから、読み出し速度がCCDと同じと仮定すると、CMOSイメージセンサは原理的にCCDよりもノイズレベルが画素とカラム読み出し回路の割合だけ高いことになる[1]。これがCCDに比べてCMOSイメージセンサのノイズが高いといわれるゆえんである。なお、CMOSイメージセンサはこれら以外に素子ばらつきによる固定パターンノイズが重畳するが、現在はCDSと

いう技術によりほぼ問題ないレベルまで解決できている。

以上のことから、CMOSイメージセンサの支配的なノイズは帯域の広いバッファのノイズであることがわかる。このバッファで発生するノイズを低減することで支配的なランダムノイズを抑制し、低照度でのダイナミックレンジを確保する。

このノイズ抑制方法の基本原理は至極単純である。CMOS イメージセンサの機能 回路を集積可能である点に注目し、カラムに信号を増幅する回路をもうける。この信号増幅で、バッファで重畳される支配的なノイズを相対的に小さく見せることで信号のノイズ耐性を高めることが可能である。ここで問題となるのが入力信号をゲイン倍 (M 倍) 増幅すると仮定すると、増幅後に加わるノイズは入力換算で 1/M に抑制されるが、信号のダイナミックレンジも 1/M に抑制されてしまうことである。これはセンサの信号が極小さな振幅しかないとすれば有効な方法であるが、たいていの場合はカラム増幅段の出力が飽和し、十分な S/N が取れない。この問題は、カラムで適応的に増幅することで解決する。すなわち、画素からの信号が小さくノイズに対して信号を増幅しても飽和しない場合は後段に接続される読み出し回路からのノイズの影響に耐性を持たせるために高いゲインで増幅する。一方、画素からの信号が十分大きくノイズに対して耐性がある場合は低いゲインで増幅しダイナミックレンジを確保する。

これらの機能回路は、1bit の比較器とゲイン可変のカラムアンプにより実現する。また、カラムと画素でどの程度ランダムノイズが重畳するかをノイズのスペクトル密度 (PSD) と伝達関数より算出した。ノイズ解析の結果、カラムで増幅するとカラム以降のランダムノイズはその増幅倍率で入力換算すことで低減できることは明らかであるが、カラム増幅器自身が発生するノイズについても低減できることがわかった。

以下に、回路構成について述べ、その構成におけるランダムノイズの解析について述べる。最後に実際に作成したチップの測定結果を述べる。

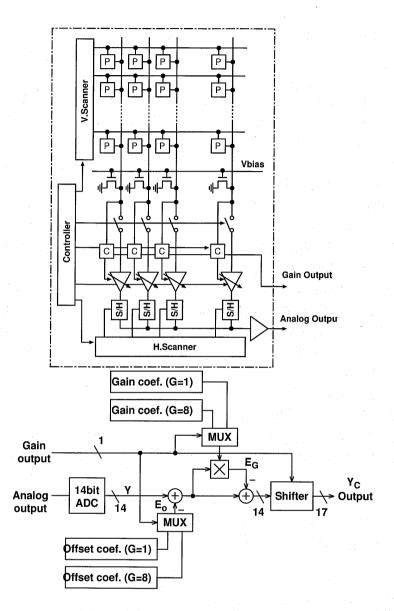

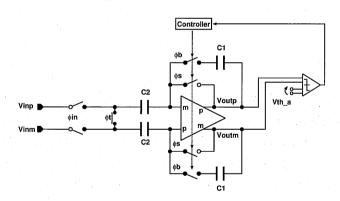

# **3.2** 適応ゲインカラム増幅に基づく CMOS イメージセンサの構成

提案する適応ゲインカラムアンプに基づく CMOS イメージセンサの構成を図 3.1 に示す。画素部、適応ゲインカラム増幅器、サンプルホールド回路、最終読み出しアンプをから構成され、これらを 1 チップに集積化した。外部回路として 14bitA/D 変換器 (AD9240,AnalogDevices) を使用し、デジタル補正回路を FPGA(Field Programmable Gate Array) で作成した。画素構造は CMOS イメージセンサ専用プロセスを使用し、埋め込みフォトダイオードを用いている。

図 3.1: イメージセンサブロック図

# 3.3 画素回路

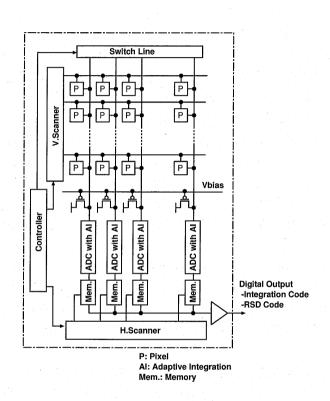

画素部は CMOS イメージセンサ専用プロセスを用いて埋め込みフォトダイオード [2] [3] を使用し、4Tr 方式とした。図を 3.2 に示す。

図 3.2: 画素部回路図

# 3.4 適応ゲインカラム増幅回路

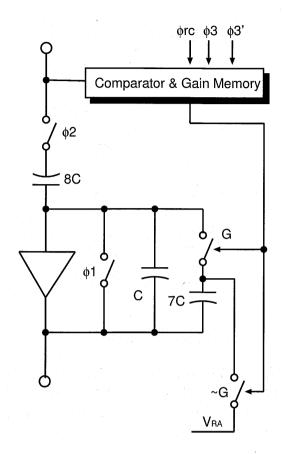

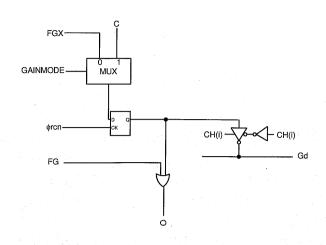

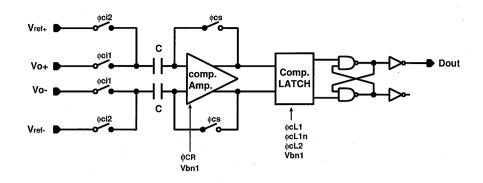

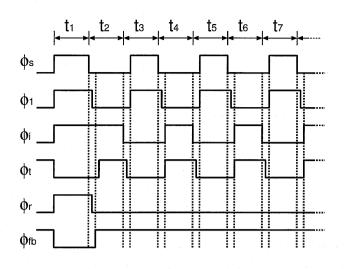

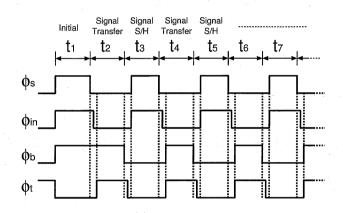

適応ゲインカラム増幅回路の構成要素としては、増幅回路のコア回路である高ゲインのアンプ、入力信号のレベルを判定するコンパレータ、ゲインを記憶するゲインメモリからなる。図 3.3 に適応ゲインカラム増幅部の全体図を、また図 3.4 にはそのタイミングチャートを示す。

動作は、順に

- 画素リセットレベルのサンプルをカラム回路が行う

- カラム回路への信号を切り離し、コンパレータへ画素信号レベルを入力し判定

- カラム回路のゲインの設定、設定したゲインの記憶

- 画素信号レベルをカラム回路へ入力し信号増幅、後段 S/H 回路へ出力し記憶となる。以下、各々の回路について詳細を述べる。

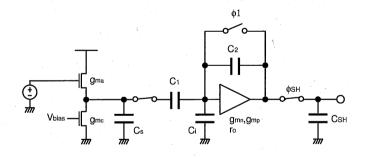

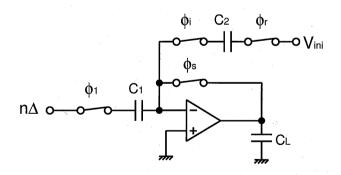

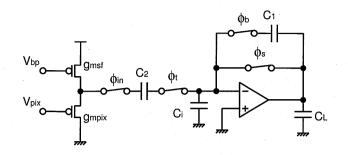

## 3.4.1 カラム増幅回路

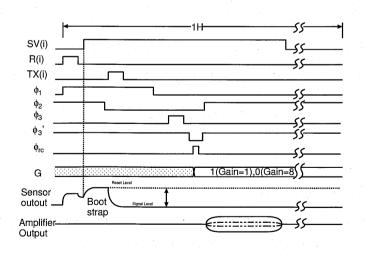

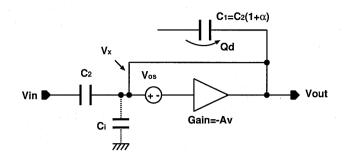

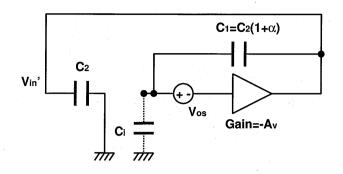

カラム増幅回路は2章でも説明をしたスイッチトキャパシタ回路を用いた。図3.5 にカラムに用いるスイッチトキャパシタ回路を示す。スイッチトキャパシタの動作であるが、入力を画素信号に見立てて動作を追う。まず、スイッチ  $\phi$  を ON し、アン

図 3.3: 適応ゲインカラム増幅部:全体図

図 3.4: 適応ゲインカラム増幅部:タイミング図

図 3.5: スイッチトキャパシタ回路

プの入出力をショートしショート電圧  $V_s$  にする。この時、回路の入力は画素回路のリセット電圧  $V_R$  である。容量  $C_1$  には式 3.1

$$Q = C_1 \cdot (V_s - V_R) \tag{3.1}$$

の電荷が蓄積される。その後、スイッチ $\phi$ を OFF する。このままでは入力の変化がないので出力はショート電圧  $V_s$  のままであるが入力が画素回路の信号レベル  $V_{sig}$  に変化すると電荷保存の法則より、式 3.2 となる。

$$Q = C_1 \cdot (V_s - V_{sig}) + C_2 \cdot (V_s - V_{out}) \tag{3.2}$$

以上の式から、

$$V_{out} = -\frac{C_2}{C_1}(V_{sig} - V_R) + V_s \tag{3.3}$$

結果から、出力される賞味の信号  $\Delta V_{sig}$  はリセット電圧と信号電圧の差電圧であり、これは固定パターンノイズと画素からのリセットノイズをキャンセルできる相関二重サンプリングの動作を示している。式より、キャパシタの容量比  $C_2/C_1$  の係数で正味の信号  $\Delta V_{sig} = (V_{sig} - V_R)$  増幅されて出力されることが分かる。この容量比を入力電圧の大きさに対し適応的に増幅させることにより適応ゲインカラム増幅を行う。なお、アンプのショート電圧  $V_s$  は各カラムごとにばらつくが、これは外部のデジタル FPN キャンセルで除去を行う。通常、デジタル領域で除去を行う場合、そのデジタルダイナミックレンジ (分解能) が FPN に比べて大きいと FPN が十分に除去できない。本方式は最大 17bit のダイナミックレンジを持つためにデジタル領域での FPN 除去が可能である。

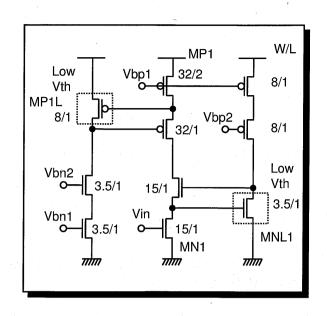

#### 3.4.2 増幅器

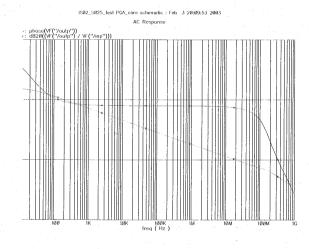

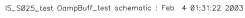

図 3.6 に増幅器の回路図を、また図 3.7 に出力に負荷容量  $C_L=1.25pF$  を接続した場合の特性を示す。

図 3.6: ゲインブーストカスコード増幅器

図 3.7: 増幅器の特性

増幅器、アンプには PMOS、NMOS 各々 2 段のカスコード接続を用い、さらにゲインを向上させるために、ゲインブースト回路を組み込んだ。通常のゲインブーストでは、ブースト回路の入力のトランジスタを飽和領域で動作させる必要がある。もし、線形領域で動作させるとゲインが極端に低下する。通常は回路図 3.6 中心にある最上段、最下段の PMOS(P1) と NMOS(N1) は飽和領域で動作しているが、そのドレイン-ソース間電圧は  $Vds_{MP1}$ 、 $Vds_{MN1}$  ともども、通常約 0.3V 程度である。この電圧は左右にあるブーストされるトランジスタ (MNL1, MPL1) のゲートに入力される。これは一般的なトランジスタのスレッショルド電圧である  $0.5V\sim0.7V$  には及

ばない。通常のカスコードと同等の出力振幅を得るために、回路3.6では

$$Vgs_{MNL1} = Vds_{MN1} \ge Vth_{MNL1} \tag{3.4}$$

$$Vqs_{MPL1} = Vds_{MP1} \ge Vth_{MPL1} \tag{3.5}$$

でなければならない。この式は、入力トランジスタの $Vds_{MN1}$  と電流源トランジスタ  $Vds_{MP1}$  でブーストトランジスタの入力電圧  $Vgs_{MLN1,Vgs_{MLP1}}$  を、アンプとして動作する飽和領域で動作させなければならないことを示している。このトランジスタに通常のトランジスタを使用すると、ブースト側のトランジスタが飽和領域で動作しない。そこで、ブースト側のトランジスタを他のトランジスタより小さい LowVthのトランジスタを用いることにより、低いゲートバイアスでトランジスタを ON(飽和領域で動作)させる。この構成により、広い出力フルスケールを得て、トランジスタの Open Loop ゲイン 100dB 以上、位相余裕 90 度を達成した。この特性は提案するカラムアンプの構成に十分な性能である。

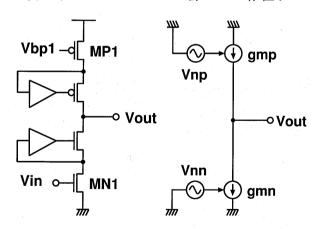

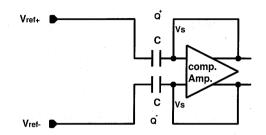

#### 3.4.3 比較器

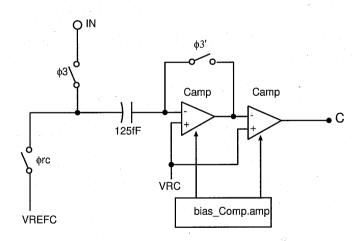

図3.8 に比較器の回路図を示す。比較器(コンパレータ)は入力電圧を参照電圧と 比較する回路である。内部回路は、入力に用いるカップリングのための容量と低ゲインのオペアンプである。これを図3.9 に示す。

図 3.8: 比較器

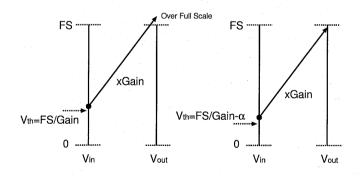

フラッシュ型の A/D 変換器等に組み込まれる高精度のコンパレータと比較して、このコンパレータは低照度と高照度のどちらにあるかを、適応ゲインアンプによる演算結果がフルスケールを外れない範囲で比較すれば良い。図 3.10 に入力信号と閾値レベルに対する出力信号のレベルを示す。例えば閾値をフルスケール (FS) の増幅

図 3.9: 比較器内部のアンプ

倍 (Gain) で割った値に設定した場合は、図 3.10 の左側に示すように入力信号が閾値を超えた場合に比較器が誤判定を起こすと、FS を超えて信号に非線形性が発生する。一方、図 3.10 の右側に示すようにこの閾値を、FS を Gain で割った値よりも少し低い値に設定することで誤判定が生じた場合でも出力信号が FS を超えないようにすることが可能である。このように、入力信号の増幅される範囲は閾値レベルを下げた割合だけ減少するが、比較器は精度を必要とせず回路が簡素化されるため小さな面積で実現可能である。

図 3.10: 比較器の誤判定を考慮した判定レベル

比較器の動作であるが、リセットレベルを前述のカラムアンプで記憶しのち、入力スイッチ  $\phi_2$  を切り  $\phi_3$  を ON し、信号レベルをサンプルする。信号レベル  $V_{sig}$  を比較器の容量に記憶させ  $\phi_3$  を OFF し、続いて  $\phi_3$  を OFF し、アンプをショート電

圧から解放する。その後に、 $\phi_{rc}$  を ON し、電圧を  $V_{refc}$  と比較する。コンパレータの出力 C は

$$C = \begin{cases} 1 & V_{sig} < V_{REFC} \\ 0 & V_{sig} \ge V_{REFC} \end{cases}$$

(3.6)

となる。

高速でない一般的なコンパレータは、図3.9のような構成ではなく差動のアンプの代わりに、インバータで構成される。しかし、ゲインが反転するときに電源グランド間に瞬間的な電流が流れる。これはインパルス的な電流であるので広帯域までそのスペクトルを持ち、他の回路への電源を介してのノイズの混入が問題となる。コンパレータの内部回路にインバータではなく、アンプを組み込むことにより、電源からのノイズを抑制する効果も得られる。また、インバータの場合はゲインの判定がつきにくい場合、 $V_{sig} = VREFC$ の状態の場合、メタステーブルという準安定状態が存在し、ゲイン判定のエラーとなるが、コンパレータ内部のアンプのショート電圧は次段に接続されるメモリ回路において電位的に Lo の位置に来るよう設計したので、ゲイン判定のミスがない。

#### 3.4.4 ゲインメモリ

ゲインメモリは、判定されたゲインを記憶する素子であり、アナログ出力とともにチップ外に水平スキャン信号 CH(i) により同期出力される。図 3.11 にゲインメモリ部を示す。メモリは、デジタル回路の D-Latch を用いた。まず、制御信号の GAINMODE と FGX により、適応モードと通常モードを切り替えを可能にし、通常モード時には外部 FGX により、1倍もしくは 8 倍に固定できるよう設計した。また、アンプリセット時には強制的に容量をアンプとショートさせておくようにし、回路の誤動作、ならびに 1 ライン前の状態に回路が影響しないようにした。強制的に容量をアンプとショートする動作を組み込まないと、次の演算の時に容量に残る残留電荷が履歴となって次のフレームに影響を及ぼす。

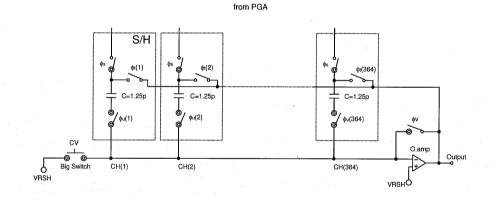

## **3.4.5** S/H、バッファ部

図 3.12 にサンプルホールド回路、図 3.13 にそのタイミング図、3.14 にバッファアンプの回路を示す。サンプルホールド回路はアンプの出力を容量に蓄積し、それをアンプの入出力に順次走査しながら接続することにより実現する。カラムアンプから信号が出力されている間  $\phi_u$  全てのスイッチを ON し、サンプルする。その時、アンプの駆動を補助するスイッチ CV も ON する。このスイッチは信号のホールドをする前に接続を切る。信号は  $\phi_s$  を OFF することによりホールドされる。そののち

図 3.11: ゲインメモリ部

に、 $\phi_u(i)$ 、 $\phi_t(i)$  を順次走査する。なお、このスイッチはハザードが出ると信号の劣化につながるので各パルスは信号の遅延を利用しアンオーバーラップさせている。

図 3.12: S/H 部

バッファアンプは信号を増幅する最終段のアンプである。アンプは 2 つあり、信号増幅用のアンプと同じ構成のもので、出力ドライブ用のアンプを設計した。アーキテクチャは低ノイズ化のために PMOS 入力とし、出力フルスケールを広くするために差動のフォールデットカスコードを用いた。図 3.15 に出力に I/O パッドと外部の測定基板の寄生容量を加味した 20pF の容量がついた状態でのバッファアンプの特性を示す。ゲインは 62dB であり、位相余裕は 75 度である。この特性は、回路の動作には十分足りる帯域とゲインである。

図 3.13: S/H タイミング図

図 3.14: バッファアンプ

図 3.15: バッファアンプの特性

## 3.5 適応ゲインカラムアンプの特性

図3.16 に前述の回路構成でSPICEシュミレーションをし、ゲインを1倍、2倍、4倍、8倍と適応的に増幅させた場合の出力特性とゲインを復調した特性を示す。シュミレーション時に使用した容量のパラメータは以下の通りである。

|            | 変数                  | 値                  |

|------------|---------------------|--------------------|

| アンプ入力側容量   | C1                  | 2pF                |

| フィードバック容量  | C2                  | 2pF/Gain           |

| コンパレータ入力容量 | $C_{comp}$          | 125fF              |

| アンプ出力容量    | $\operatorname{CL}$ | $1.25 \mathrm{pF}$ |

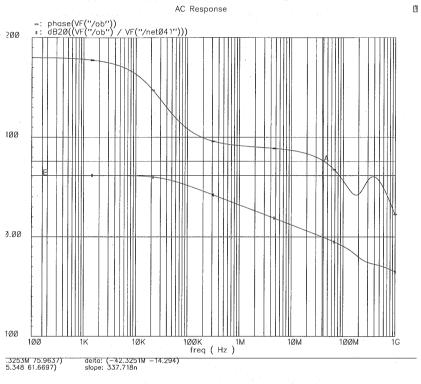

また、その直線性誤差を 3.17 に示す。 直線性誤差から、10bitLSB 以内に収まって

図 3.16: 適応ゲインカラムアンプの特性

図 3.17: 非直線性誤差

いるので人間の目で見てもゲイン復調時の非線型誤差は問題ない (40dB以下) と言える。シミュレーションのデータはゲインを1倍から8倍まで適応的に設定しているが、今回の試作は、カラム高ゲイン増幅における低ノイズ化が有効であるということを証明するものであり、試作は1倍と8倍のみで行った。

## 3.6 適応ゲインカラム増幅器のノイズの見積もり

#### 3.6.1 はじめに

カラムで信号を増幅すると、増幅後の信号に後段で接続される読み出し回路から重畳するランダムノイズに対して耐性を持たせることができることは容易に理解できる。しかしながら、画素とカラムで発生するランダムノイズが支配的であるとカラムで増幅する意味をなさない。カラムでの帯域は最終読み出し部の帯域よりも狭いが、我々が必要とするのは具体的に何  $\mu V$  のノイズがカラムで重畳するのかという値である。

従って、画素とカラムアンプにおいて実際にノイズがどの程度重畳するかを見積 もることが重要となる。

今回用いた回路は入力側と帰還側の容量比で信号を増幅するスイッチトキャパシタ回路を用いているので、この回路のノイズ解析を行う必要がある。この解析方法は、文献 [4] [5] よりも、CMOS イメージセンサのランダムノイズの解析方法としての文献 [6] に詳じく記述してある。基本的には、ノイズの PSD(power spectrum density)とその伝達関数がわかれば求まる。しかしながら、スイッチトキャパシタの場合の解析方法が少し複雑であるので、引用のみで計算結果を述べたところで理解は難しい。従って、ここでランダムノイズの見積方法を例を挙げて記述する。

最初は、まず簡単のために容量Cで帯域制限された場合のノイズについて記述する。続いて、スイッチトキャパシタ回路の場合の解析方法を述べ、最後に提案する適応ゲインカラム増幅での場合のランダムノイズを見積もる。なお、この解析手法は他の章でも用いている。

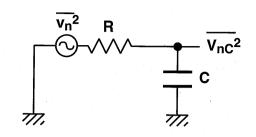

#### 3.6.2 容量 C で帯域制限されたノイズ

まず始めに、単純に容量Cで帯域制限されたノイズについて考える。

熱雑音は抵抗成分 R があるとそこに単位周波数あたり  $4kTR/\Delta f$  のノイズが発生することは述べた。もし、回路が極を持たない抵抗 R のみの回路で記述できるならば、抵抗 R が無限の周波数帯域、すなわち無限の大きさのノイズを発生していることになる。しかしながら、実際の回路は配線容量や演算のための容量など至る所に容量 C が寄生容量などの形で回路に接続される。これは、分布定数回路として回路

図 3.18: Cで帯域制限される雑音

図 3.19: Cで帯域制限された雑音電力スペクトル

を見るのではなく、支配的な容量が集中定数回路として接続されていると考える。結果として、図 3.18 に示すようにランダムノイズは配線に接続される支配的な容量によりその帯域が図 3.19 のように制限されるので、ノイズの大きさ (ノイズ電力、振幅) が制限される。

ランダムノイズを求めるのに必要なのはノイズの PSD と、ノイズ源からの伝達関数であるので、図 3.18 回路の入力からの出力での伝達関数を求めると

$$H_n(\omega) = \frac{1}{1 + i\omega CR} \tag{3.7}$$

ノイズは電力で考えるので、ノイズ電力に関する伝達関数  $|H_n(\omega)|^2$  は、

$$|H_n(\omega)|^2 = \frac{1}{1 + (\omega CR)^2}$$

(3.8)

となる。この伝達関数によりノイズ電力が帯域制限される。この時の雑音スペクトルを図 3.19 に示し、これを全周波数に渡って積分すると、容量で帯域制限された平均雑音電力が求まる。

$$\overline{v_{nC}^2} = S_n \int_0^\infty |H_n(\omega)|^2 df = 4kTR \int_0^\infty \frac{1}{1 + (\omega CR)^2} df$$

(3.9)

$x = \omega CR$  と置いて変数変換すると、 $df = \frac{1}{2\pi CR} dx$  であるので

$$\overline{v_{nC}^2} = 4kTR \int_0^\infty \frac{1}{1 + (\omega CR)^2} \frac{1}{2\pi CR} dx = \frac{2kT}{\pi C} \int_0^\infty \frac{1}{1 + x^2} dx$$

(3.10)

ここで、

$$\int_0^\infty \frac{1}{1+x^2} dx = [tan^{-1}(x)]_0^\infty = \frac{\pi}{2}$$

(3.11)

より、

$$\overline{v_{nC}^2} = \frac{kT}{C} \tag{3.12}$$

を手計算により得ることができる。この式の結果から、熱雑音の電力はその雑音源となる抵抗 R には関係なく、容量 C で決定される。求まったノイズ電力より、ノイズの実効電圧は  $\sqrt{kT/C}$  となる。

S/H 回路にサンプルされたノイズはその出力の伝達関数を求めると、アパーチャ効果が現れ、またさらにナイキスト周波数以上のノイズの折り返しが起こる [5] [7]。しかし、S/H 回路に"サンプルされた"ノイズ電圧は、その波形を直接観測しない限り  $\sqrt{kT/C}$  のままでよい。

したがって、S/H 回路にサンプルされる雑音は抵抗と容量でフィルタされた 2 乗雑音と同様に  $\sqrt{kT/C}$  で一定になる。具体的な数値では、容量に 1pF を用いた場合に標準偏差が約  $64\mu V_{rms}$  のノイズが重畳することを意味する。

### 3.6.3 スイッチトキャパシタ回路でのノイズ

容量Cで帯域制限されている場合のノイズの見積もりは、積分が手計算可能な式であったために求めることが可能である。実際の回路は厳密に解を解こうとすると、抵抗、容量、アンプの回路網の伝達関数を解く必要があり、手計算では現実的に困難である。このことから、実際にノイズ電力を求めるには、計算機による数値計算により伝達関数の解を導くことになる。

スイッチトキャパシタ回路で発生するノイズは大きく分けて2つある。一つは、入力信号をサンプルしている間にスイッチトキャパシタのアンプの入力ノードに蓄積されたノイズ電荷が入力信号のサンプル終了とともに出力に転送される"サンプル転送ノイズ"と、転送された後に回路が出力ノードにノイズを直接出力する"直接出力ノイズ"がある。これは、スイッチトキャパシタが時間別に信号サンプル、信号転送といった別処理を行うために回路の接続状態が切り替わる時点においてノイズを発生して、そのノイズが後の動作まで残留するためである。

スイッチトキャパシタに限った場合の実際のノイズ計算を以下のフローにまとめた。まず、"サンプル-転送ノイズ"は

1. 信号サンプル状態での各々のノイズ源を特定し、ノイズ源の PSD を求める。

- 2. 各々のノイズ源から特定のノード(アンプの入力)への伝達関数を求める

- 3. PSDと伝達関数の積分より特定のノードに蓄積されるノイズ電荷を求める。

- 4. 特定のノードに蓄積されたノイズ電荷が、回路の転送モードですべてフィード バックキャパシタに転送されると考えて出力されるノイズを計算する。

で求まる。特定のノードとは、ノイズ電荷の蓄積が行われるアンプの入力ノードのことを表す。つづいて"直接出力ノイズ"は、

- 1. 信号転送状態での各々のノイズ源を特定し、ノイズ源の PSD を求める。

- 2. 各々のノイズ源から出力への伝達関数を求める。

- 3. PSD と伝達関数の積分より回路から出力されるノイズを求める。

で求まる。最終的に、これらのノイズが独立であることから単純に電力領域で加算をすればトータルの雑音がどれほど重畳するかが具体的な数値としてわかる。以下に、この手順に従ってランダムノイズの見積もりを計算する。

#### サンプル-転送ノイズ

まず、アンプの入力にノイズ電荷が蓄積しそれが次の転送フェーズで転送される ノイズについて考える。

図3.20に解析する回路図を示す。この回路の信号サンプル時の等価回路を図3.21に

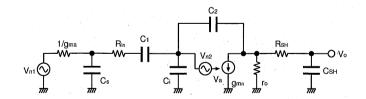

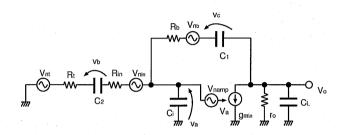

図 3.20: 画素と適応ゲイン増幅器の回路図

示す。

まず、この状態でのノイズの PSD を求める。ノイズ源は

- アンプの入力側スイッチ  $(R_{in})$

- アンプの入力トランジスタ  $(q_{mn})$

図 3.21: 画素と適応ゲイン増幅器の入力信号サンプル時の等価回路

- アンプのフィードバックに接続されるスイッチ  $(R_{on})$

- ・ アンプの出力側スイッチ (R<sub>SH</sub>)

の5つを考慮する。スイッチが発生する PSD はそれぞれ

$$Sn_{in} = 4kTR_{in} (3.13)$$

$$Sn_{on} = 4kTR_{on} (3.14)$$

$$Sn_{SH} = 4kTR_{SH} (3.15)$$

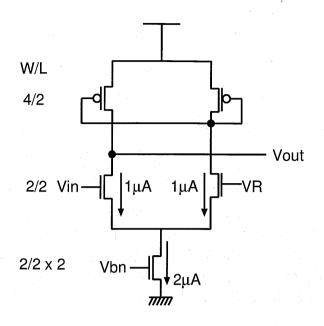

と求まる。一方、トランジスタの PSD は単純に  $\frac{8}{3}kT\frac{1}{gm}$  とは求まらない。これは入力トランジスタ以外に、カスコード接続の電流源トランジスタもノイズ源となるためである。図 3.22 にカラムの回路図と、支配的なノイズ源を考えた場合の等価回路を示す。

この場合、アンプで発生するノイズのノイズ源は2つ存在するので計算がやや複雑

図 3.22: カラムアンプのノイズ源

になる。一般には単純化するために入力側のトランジスタのみがノイズを発生しているように電流源側のノイズを入力換算し、ノイズ源を1つにする。以上のことか

ら、アンプで発生するノイズの PSD は入力トランジスタのトランスコンダクタンス を  $g_{mn}$ 、電流源側を  $g_{mp}$  とすると

$$Sn_{amp} = Sn_{mn} + Sn_{mp} \left(\frac{g_{mp}}{g_{mn}}\right)^2 \tag{3.16}$$

$$= \frac{8}{3}kT\frac{1}{g_{mn}} + \frac{8}{3}kT\frac{1}{g_{mn}}\left(\frac{g_{mp}}{g_{mn}}\right)^2 \tag{3.17}$$

$$= \frac{8}{3}kT\frac{1}{q_{mn}}(1+\frac{g_{mp}}{q_{mn}}) \tag{3.18}$$

と求まる。画素で発生するノイズも同様に画素のトランジスタのトランスコンダクタンスを  $g_{ma}$ 、画素のソースフォロワのトランスコンダクタンスを  $g_{mc}$  とすると

$$Sn_{pix} = Sn_a + Sn_{sf} \left(\frac{g_{mc}}{g_{ma}}\right)^2 \tag{3.19}$$

$$= \frac{8}{3}kT\frac{1}{g_{ma}} + \frac{8}{3}kT\frac{1}{g_{mc}}\left(\frac{g_{mc}}{g_{ma}}\right)^2 \tag{3.20}$$

$$= \frac{8}{3}kT\frac{1}{g_{ma}}(1 + \frac{g_{mc}}{g_{ma}}) \tag{3.21}$$

と記述できる。

次に、各々の伝達関数を求める。伝達関数は計算機より容易に求めることができる。これは、AC解析でアンプの入力ノードをノイズ源と見立てた交流信号源の入力ノードで除算すれば求まる。

続いて、各ノイズ源が発生するアンプの入力に蓄積するノイズ電荷を求める。ここで、 $H_{xy}$ をノイズ源 x からキャパシタ y への伝達関数、ソースフォロワトランジスタが発生するノイズ電荷を  $Qn_a$ 、アンプの入力側スイッチが発生するノイズ電荷を  $Qn_{in}$ 、アンプの入力トランジスタが発生するノイズ電荷を  $Qn_n$ 、アンプのフィードバックに接続されるスイッチが発生するノイズ電荷を  $Qn_o$ 、アンプの出力側スイッチが発生するノイズ電荷を  $Qn_o$ 、アンプの出力側スイッチが発生するノイズ電荷を  $Qn_o$

$$Qn_{a}^{2} = Sn_{pix} \int_{0}^{\infty} (C_{1}^{2}H_{a}^{2} + C_{2}^{2}H_{a}^{2} + C_{i}^{2}H_{a}^{2} + C_{i}^{2}H_{in}^{2} +$$

$$+2C_{1}C_{2}Re\{H_{n} \ _{1}^{*}H_{n} \ _{2}\} + 2C_{1}C_{i}Re\{H_{n} \ _{1}^{*}H_{n} \ _{i}\}$$

$$+2C_{2}C_{i}Re\{H_{n} \ _{2}^{*}H_{n} \ _{i}\})df$$

$$Qn_{on}^{2} = Sn_{pix} \int_{0}^{\infty} (C_{1}^{2}H_{on}^{2} \ _{1} + C_{2}^{2}H_{on}^{2} \ _{2} + C_{i}^{2}H_{on}^{2} \ _{i}$$

$$+2C_{1}C_{2}Re\{H_{on} \ _{1}^{*}H_{on} \ _{2}\} + 2C_{1}C_{i}Re\{H_{on} \ _{1}^{*}H_{on} \ _{i}\}$$

$$+2C_{2}C_{i}Re\{H_{on} \ _{2}^{*}H_{on} \ _{i}\})df$$

$$Qn_{SH}^{2} = Sn_{pix} \int_{0}^{\infty} (C_{1}^{2}H_{SH}^{2} \ _{1} + C_{2}^{2}H_{SH}^{2} \ _{2} + C_{i}^{2}H_{SH}^{2} \ _{i}$$

$$+2C_{1}C_{2}Re\{H_{SH} \ _{1}^{*}H_{SH} \ _{2}\} + 2C_{1}C_{i}Re\{H_{SH} \ _{1}^{*}H_{SH} \ _{i}\}$$

$$+2C_{2}C_{i}Re\{H_{SH} \ _{2}^{*}H_{SH} \ _{i}\})df$$

$$(3.26)$$

と相関の項を考慮した各ノイズ源がアンプの入力に蓄積するノイズ電荷の式が得られる。

最後に、これらのノイズ電荷がスイッチトキャパシタの転送フェーズですべて帰還容量 $C_2$ に転送されると考えるとサンプル-転送ノイズで発生するノイズ電荷を $Qn_{ST}$ 、その結果発生するノイズ電圧を $\overline{vn_{ST}}$ とすると

$$Qn_{ST}^2 = Qn_a^2 + Qn_{in}^2 + Qn_n^2 + Qn_{on}^2 + Qn_{SH}^2 (3.27)$$

$$\overline{vn_{ST}^2} = \frac{Qn_{ST}^2}{C_2^2}$$

(3.28)

と求まる。 $\overline{vn_{ST}^2}$ の平方根を取ることでサンプル-転送ノイズで発生するノイズの標準偏差が求まる。

#### 直接サンプルノイズ

続いて、スイッチトキャパシタ回路が信号転送フェーズで出力するノイズについて考える。このフェーズでの等価回路を3.23に示す。このフェーズで出力されるノイズは、各ノイズ源が直接スイッチトキャパシタ回路の出力部に出力するノイズである。まず計算フローに従い、まず各々のノイズ源のPSDを算出する。等価回路図

図 3.23: 画素と適応ゲイン増幅器の信号転送時の等価回路

3.23より、ノイズ源はサンプル-転送ノイズで計算したフィードバックスイッチの抵

抗  $R_{on}$  以外のノイズ源がそのまま直接サンプルノイズのノイズ源となる。従って各々の PSD は

$$Sn_{pix} = \frac{8}{3}kT\frac{1}{g_{ma}}\left(1 + \frac{g_{mc}}{g_{ma}}\right) \tag{3.29}$$

$$Sn_{amp} = \frac{8}{3}kT\frac{1}{g_{mn}}\left(1 + \frac{g_{mp}}{g_{mn}}\right) \tag{3.30}$$

$$Sn_{in} = 4kTR_{in} (3.31)$$

$$Sn_{SH} = 4kTR_{SH} (3.32)$$

と記述できる。

次に伝達関数を求めるが、計算機による等価回路のAC解析でノイズ源から回路の出力部までの周波数特性から容易に求まる。

最後に、各々のノイズ源が回路の出力部へ発生するノイズを計算する。ソースフォロワトランジスタが発生するノイズ電圧を $vn_a$ 、アンプの入力側スイッチが発生するノイズ電荷を $vn_{in}$ 、アンプの入力トランジスタが発生するノイズ電荷を $vn_n$ 、アンプのフィードバックに接続されるスイッチが発生するノイズ電荷を $vn_{on}$ 、アンプの出力側スイッチが発生するノイズ電荷を $vn_{SH}$ とすると

$$\overline{vn_a^2} = Sn_{pix} \int_0^\infty H_{a\ o}^2 df \tag{3.33}$$

$$\overline{vn_{in}^2} = Sn_{in} \int_0^\infty H_{in\ o}^2 df \tag{3.34}$$

$$\overline{vn_n^2} = Sn_{amp} \int_0^\infty H_{n\ o}^2 df \tag{3.35}$$

$$\overline{vn_{SH}^2} = Sn_{SH} \int_0^\infty H_{SH\ o}^2 df$$

(3.36)

と平均 2 乗雑音として記述することができる。ここで  $H_x$   $_o$  はノイズ源  $_x$  から回路出力部までの伝達関数である。

最終的に直接サンプルされるノイズ vnps は

$$\overline{vn_{DS}^2} = \overline{vn_a^2} + \overline{vn_{in}^2} + \overline{vn_n^2} + \overline{vn_{SH}^2}$$

(3.37)

より $\overline{vn_{DS}^2}$ の平方根を取ることで、このノイズの標準偏差を求めることができる。

## 3.6.4 適応ゲインカラム増幅器のノイズの計算例

以上のノイズ解析の結果からランダムノイズを計算して見積もる。等価回路での伝達関数の見積もりは SpectreS を用い、積分には Matlab の台形近似積分関数 (trapz())を用いた。各々の見積もりのためのパラメータを表 3.1 に示す。

ここで、パラメータ $R_{SW}$ であるがこれは図3.24のように画素からのノイズを分離し、純粋にカラムアンプのみで発生するノイズを計算するためにテストモードで動

表 3.1: ノイズ解析のためのパラメータ

| Gain (gain of column amplifier)                        | 1, 2, 4, 8, 16          |

|--------------------------------------------------------|-------------------------|

| $g_{ma}$ (transconductance of floating diffusion)      | $41.8 \ \mu\Omega^{-1}$ |

| $g_{mc}$ (transconductance of current mirror)          | $144~\mu\Omega^{-1}$    |

| $g_{mn}$ (transconductance of column amplifier (nMOS)) | $56.9 \ \mu\Omega^{-1}$ |

| $g_{mp}$ (transconductance of column amplifier (pMOS)) | $76.7 \ \mu\Omega^{-1}$ |

| $R_{on}$ (on-resistance of feed-back switch)           | $1~\mathrm{k}\Omega$    |

| $R_{SW}$ (on-resistance of column switch)              | 70 Ω                    |

| $R_{SH}$ (on-resistance of S/H switch)                 | $1.5~\mathrm{k}\Omega$  |

| $r_o$ (output resistance of column amplifier)          | $1.5~\mathrm{G}\Omega$  |

| $C_1$ (sampling capacitor)                             | 2 pF                    |

| $C_2$ (feed-back capacitor)                            | $C_1/Gain$              |

| $C_s$ (stray capacitance of readout tr. in the pixel)  | 574 fF                  |

| $C_i$ (stray capacitance of column amplifier)          | 92.8 fF                 |

| $C_{SH}$ (S/H capacitor)                               | $1.25~\mathrm{pF}$      |

| T (room temperature)                                   | 27 °C                   |

|                                                        |                         |

作させた場合の外部信号入力のスイッチの ON 抵抗である。この場合のノイズの計算は、ノイズ源が画素からスイッチの ON 抵抗  $R_{SW}$  に変更し計算すると求めることが可能である。

図 3.24: カラムアンプのみが生ずるノイズの計算のための回路

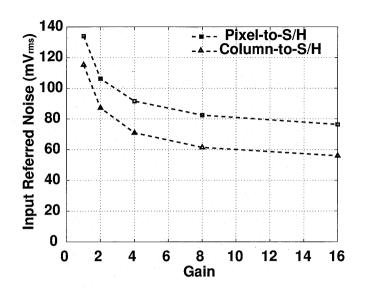

以上の計算方法とパラメータを用いて、画素とカラム読み出し回路 (スイッチトキャパシタ回路) で発生するランダムノイズと、カラム読み出し回路のみの場合のランダムノイズを計算した結果を図 3.25 に示す。結果から、ゲイン 1 倍の時で  $120\mu V_{rms}$  程度のノイズが重畳しているのがわかる。また、ゲインが高くなるにつれカラム回路、画素が生じるノイズが低減できていることがわかる。これは、カラム以降で発生するノイズは入力換算で低減できることがわかるが、カラム回路自身が発生するノイズも同時に低減できていることを示す。図 3.25 に示す解析結果から、カラムのゲイ

図 3.25: カラムの増幅率と発生するランダムノイズの関係

ンが8倍と16倍とではノイズ低減効果がほぼ同等レベルになることがわかった。

# 3.7 適応ゲインカラム増幅器を用いたイメージセンサの 試作と特性測定

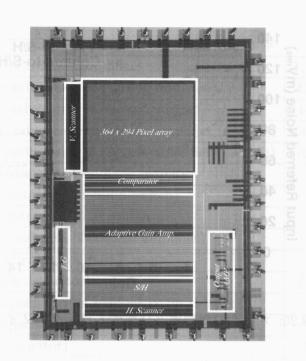

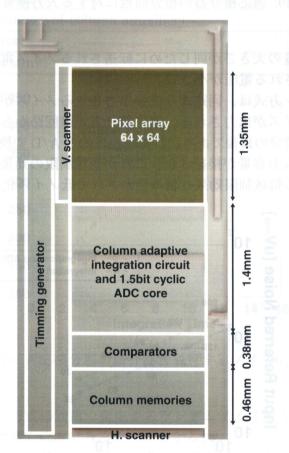

#### 3.7.1 試作したイメージセンサ

今回試作したイメージセンサを図3.26に示す。試作したチップは、CMOSイメージセンサ専用プロセスを用いた。また、先のノイズ解析の結果から、カラムのゲインは1倍と8倍の2通りに設定した。

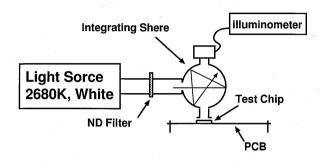

#### 3.7.2 測定環境

今回試作したイメージセンサの測定する特性は、以下の3つである。

- 入出力特性

- 固定パターン雑音

- ランダム雑音

図 3.26: 試作したイメージセンサ

測定は本研究室の測定室で行った。

使用した測定器は DC 電源 2 台とクロックジェネレータ 1 台、データ取り込みにロジックアナライザーを用いた。

| デバイス          | 製造メーカ           | 型番     |  |

|---------------|-----------------|--------|--|

| 直流電源装置        | Agilent         | E3614A |  |

| クロックパルスジェネレータ | Hewlett Packard | 81104A |  |

| ロジックアナライザ     | Hewlett Packard | 16702  |  |

測定ではデジタルローパスフィルタの代わりに、ロジックアナライザで測定したデジタルデータに対して、デジタルローパスフィルタと同等の処理を施し結果を得た。

イメージセンサのクロックタイミングは内部回路に組み込んだタイミングジェネレータによって生成させることができる、内部同期モードで測定をした。測定は全てこの内部動作モードで動作させて測定をした。イメージセンサの計測するべき特性は低照度時のノイズであるので、全て光が当たらない状態で測定を行った。

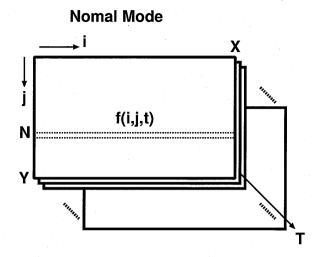

図 3.27 に測定データの配列を示す。横方向i は横の画素、縦方向j は縦方向の画素、奥方向は撮像時間(フレーム)を示す。

$$b(i) = \frac{1}{T} \sum_{t=1}^{T} \left\{ \frac{1}{Y} \sum_{j=1}^{Y} f(i,j,k) \right\}$$

(3.38)

図 3.27: 固定パターン雑音の計算

$$B(i) = \frac{1}{X} \sum_{i=1}^{X} b(i)$$

(3.39)

$$\delta_{FPN}^2 = \frac{1}{X} \sum_{i=1}^{X} \left\{ b(i) - \bar{B} \right\}^2 \tag{3.40}$$

固定パターンノイズ、FPNであるが、式3.38に示すように、カラム方向のデータを空間、時間的に積分し、カラム毎の平均値を出す。

カラム毎の平均値から、式 3.39 に示すように平均を出し、その分散を求める。これの標準偏差が固定パターンノイズである。

$$a(i) = \frac{1}{T} \sum_{t=1}^{T} \{f(i, N, t)\}$$

(3.41)

$$\bar{a(i)} = \frac{1}{T} \sum_{t=1}^{T} \left\{ \frac{1}{T} \sum_{i=1}^{X} \left\{ f(i, N, t) - a(i) \right\}^{2} \right\}$$

(3.42)

また、ランダムノイズであるが、式に示すようにある特定のラインを決め、それを 時間積分し平均を算出する。式のように、カラム方向、時間方向にその平均との差 を二乗し分散を算出する。得られた値より、標準偏差を計算することでランダムノ イズが求まる。

ノイズキャンセルをした固定パターンノイズは図、3.28 に示すように FPN 測定モードで測定を行う。これは、センサをテストモードに切り替えてセンサからの信号線に外部から直接 DC 電圧を入力し、純粋にアンプ以降の固定パターンノイズを式 3.43 に示すように求める。

図 3.28: ランダム雑音の計算

$$\bar{c(i)} = \frac{1}{T} \sum_{t=1}^{T} \{f(i,t)\}$$

(3.43)

$$\bar{d(i)} = b(i) - c(i) \tag{3.44}$$

$$\bar{D} = \frac{1}{X} \sum_{i=1}^{X} d(i) \tag{3.45}$$

$$\delta_{NCFPN}^2 = \frac{1}{X} \sum_{i=1}^{X} \left\{ d(i) - \bar{A} \right\}^2$$

(3.46)

ノイズキャンセルをした固定パターンノイズは図、3.28 に示すように FPN 測定モードで測定を行う。これは、センサからの信号線に外部からバイアスを懸けて、純粋にアンプ以降の固定パターンノイズを式 3.43 に示すように求める。これを式 3.44 のように、カラムの固定パターンノイズである式 3.38 より減算を行う。これは、暗電流固定パターンノイズ成分を抽出する式である。また、暗電流固定パターンノイズの画素方向の平均をとり、暗電流固定パターンノイズを決定する (式 3.45)。最後に暗電流固定パターンノイズキャンセルをしたデータを二乗しカラムに積分し平均をとる (式 3.46) とデジタルノイズキャンセルをしたがとものと等価なノイズの分散が得られ、この標準偏差がノイズキャンセルした固定パターンノイズとなる。以下、今回の試作したイメージセンサの入出力特性とノイズの測定結果を示す。

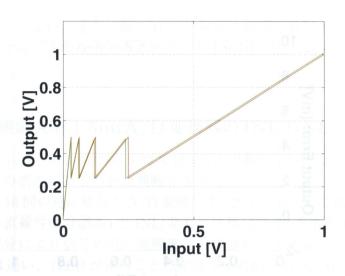

### 3.7.3 入出力特性の測定

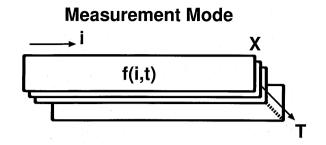

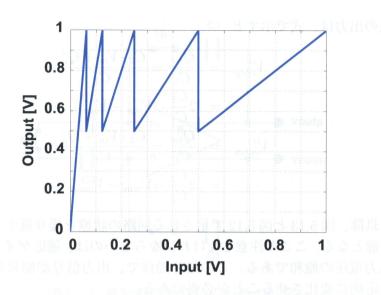

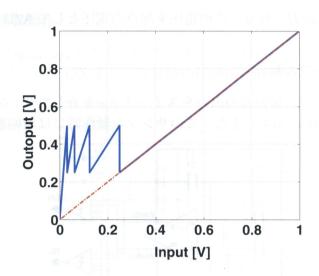

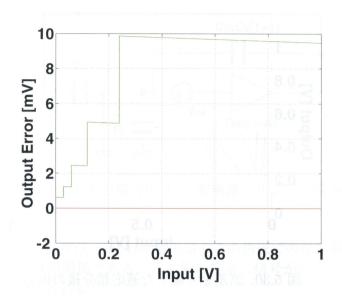

試作チップをテストモードで動作させて、カラムの増幅回路に外部より参照電圧を与えて入出力特性を測定を行った。入力信号がフルスケールである 1V の 1/10 の 100m 以下の場合は入力信号が約 8 倍で増幅されて出力される。それ以外の信号は入力信号が約 1 倍で増幅される。測定した入出力特性を図 3.29(a),(b) に示す。図の誤差はゲイン誤差であり、カラム増幅器の入力側の容量と帰還側の容量のキャパシタミスマッチによるものである。ゲインが 1 倍の場合と 8 倍の場合の両者にゲイン誤差

図 3.29: 試作したセンサのカラム回路の入出力特性

表 3.2: ゲイン誤差 (σ:誤差の標準偏差, Ave.:非線形誤差の平均値)

|                 | Without error correction     | With error correction            |

|-----------------|------------------------------|----------------------------------|

| Fullscale (G=1) | $\sigma = 0.613\%$           | $\sigma = 1.67 \times 10^{-3}\%$ |

| Gain            | $\sigma = 197 \mu \text{ V}$ | $\sigma = 184 \mu \text{ V}$     |

| switching point | Ave. $= 4.87 \text{ mV}$     | Ave. = 415 $\mu$ V               |

が存在する。また、ゲインの切り替わり時のスイッチングポイントでも非線型性が見受けられた。ゲイン誤差には自身のゲインの誤差と各カラムでのゲインのばらつきがある。表 3.2 にデジタル領域でゲイン補正を行なう前と後での場合のカラムごとのゲインの誤差と、スイッチングポイントでの誤差を示す。補正により、各カラムでのゲイン誤差が 0.63% から  $1.67\times 10^{-3}\%$  と無視できるレベルまで低減可能である。また、カラムごとにゲインが切り替わるスイッチングポイントで平均 4.87mV の非線型性が見られるが、補正をかけることで撮像時には無視できる  $415\mu V$  まで抑制できる。

## 3.8 測定結果

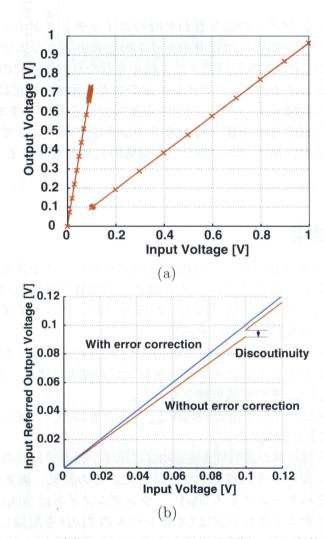

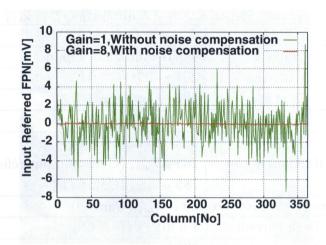

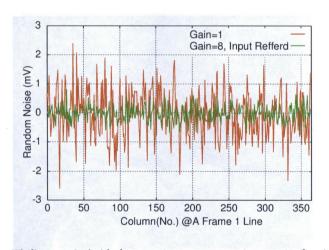

図 3.30 にゲインを 1 倍に固定した場合の固定パターンノイズと、ゲインを 8 倍に固定した場合のデジタル FPN キャンセル後の入力換算での固定パターンノイズを示す。また、3.31 にゲインを 1 倍に固定した場合のランダムノイズと 8 倍固定時のランダムノイズの入力換算したものを示す。

固定パターンノイズはゲイン 1 倍で  $2.4mV_{rms}$  だったものが、ゲイン 8 倍で入力換算処理と増幅によるデジタルダイナミックレンジの拡大により、デジタル FPN キャンセル処理で  $50\mu V_{rms}$  まで低減可能となった。

ランダムノイズはゲイン 1 倍で  $785\mu V_{rms}$  だったものが、ゲイン 8 倍の入力換算処理で  $263\mu V_{rms}$  にまで低減した。

以上の結果から得られた緒特性をを図 3.3 に示す。設計では読み出し回路でなるベくノイズが混入しないように注意して設計した。その結果、画素からのノイズが支配的となり、固定パターンノイズ  $50\mu V$ 、ランダムノイズは  $263\mu V$  という低雑音センサとなり、ダイナミックレンジは CCD レベルの 71dB を記録した。

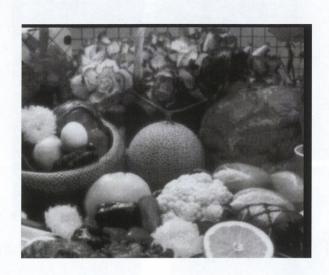

最後に、適応ゲインモード時で撮像したサンプル画像を図3.32に、その画像をゲイン復調したものを図3.33に、また、適応ゲインモードで撮像したカラー画像を図3.35に示し、その画像を復調したものを図3.35に示す。解像度は364×288のCIFフォーマットである。各々の図から、被写体の暗い部分は適応増幅により信号が8倍されていることがわかる。それらを入力換算することで、被写体の暗い部分のランダムノイズが低減された画像を取得することが可能である。

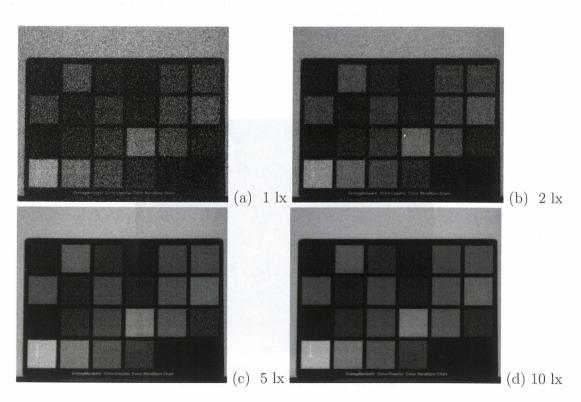

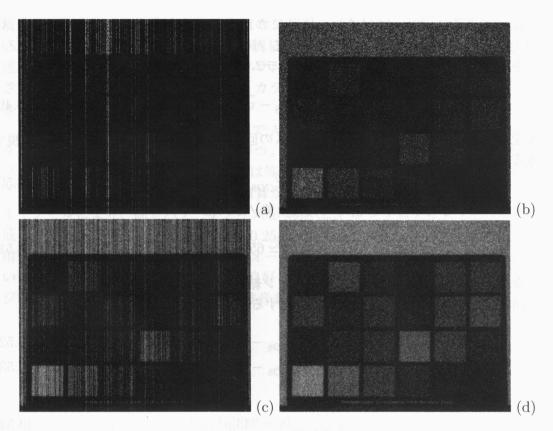

また、低照度時における撮像結果を図3.36と図3.37に示す。

図 3.30: 固定パターンノイズキャンセルの効果

図 3.31: 通常モードと適応モードでのランダムノイズの低減効果

表 3.3: 適応ゲインカラム増幅回路の特性緒言

| 1 4 74 7 4 4日中国国际 47 17 1工作日              |  |

|-------------------------------------------|--|

| $0.25~\mu\mathrm{m}$ CMOS 2P3M            |  |

| 4.3(H)mm x 5.0(V)mm                       |  |

| 364 x 294                                 |  |

| $4.95 \times 4.95 \ \mu \text{m}^2$       |  |

| 3.9 V/lx · sec                            |  |

| $2.10 \text{ mV}_{rms} \text{ (Gain=8)}$  |  |

| $263 \mu V_{rms}$ (Gain=8,input referred) |  |

| $785  \mu V_{rms}  (Gain=1)$              |  |

| $50 \ \mu V_{rms} \ (Gain=8)$             |  |

| $1.8 \text{ mV/s} (@ 60\text{C}^{o})$     |  |

| 1000 mV v z cslejši -0g g jej             |  |

| 71 dB                                     |  |

| 2.5 V single                              |  |

| 33 mW                                     |  |

|                                           |  |

図 3.32: 適応ゲインモードの画像

図 3.33: 適応ゲインモード、ゲイン復調画像

図 3.34: 適応ゲインモードのカラー画像

図 3.35: 適応ゲインモードカラー画像のゲイン復調画像

図 3.36: 低照度時における撮像例; 1lx-10lx ( $Gain=8,\,F=2.8,\,30$  frames/sec)

図 3.37: ゲイン 1 倍での低照度時の撮像例 FPN キャンセルなし (a) とあり (b)、ゲイン 8 倍で FPN キャンセルなし (c) とあり (d)(1lx, F=2.8, 30 frames/sec)

表 3.4: 試作チップのノイズ

| 公 0.4. PVIF7 7 7 477 1 7 |                           |          |                           |  |

|--------------------------|---------------------------|----------|---------------------------|--|

|                          | rms noise $(\mu V_{rms})$ |          |                           |  |

|                          | Gain = 1                  | Gain = 8 | Gain = 8 (input-referred) |  |

| Pixel to output          | 785                       | 2,104    | 263                       |  |

| Column to output         | 752                       | 917      | 114.6                     |  |

## 3.9 考察

試作したチップのゲイン 1、8 倍時のノイズとノイズ測定モードで測定したカラムアンプのみのランダムノイズの測定結果を表 3.4 に示す。これらの測定結果から、カラムで発生するノイズを見積もることができる。カラムから出力バッファまでのノイズをそれぞれのゲインで

$$\overline{v_{nCO1}^2} = \overline{v_{nC1}^2} + \overline{v_{nO}^2} \tag{3.47}$$

$$\overline{v_{nCO8}^2} = \overline{v_{nC8}^2} + \overline{v_{nO}^2} \tag{3.48}$$

と記述できる。 $\overline{v_{nCOx}^2}$  はゲイン  $\mathbf{x}$  倍時にカラムから出力を通して発生するノイズ、 $\overline{v_{nCx}^2}$  はゲイン  $\mathbf{x}$  倍時にカラムで発生するノイズ、 $\overline{v_{nO}^2}$  は読み出し部で発生するノイズを示す。これらの式から、8 倍時にカラム読み出し回路で発生するノイズは

$$\overline{v_{nC8}^2} = \overline{v_{nCO8}^2} - \overline{v_{nCO1}^2} + \overline{v_{nC1}^2}$$

(3.49)

と記述できる。ゲインが1倍時にカラムの回路で発生するランダムノイズが無視で きるとすると

$$\overline{v_{nC8}^2} \simeq \overline{v_{nCO8}^2} - \overline{v_{nCO1}^2} \tag{3.50}$$

となる。これからゲイン8倍時の入力換算ノイズは

$$\sqrt{\overline{v_{nC8}^2}}/8 \simeq 65.6[\mu V_{rms}]$$

(3.51)

となり、ランダムノイズシミュレーション結果の  $61\mu V_{rms}$  とよく一致する。 同様に、8 倍時に画素とカラムで発生するノイズを求めると

$$\overline{v_{nP8}^2} = \overline{v_{nPO8}^2} - \overline{v_{nPO1}^2} + \overline{v_{nP1}^2}$$

(3.52)

$$\simeq \overline{v_{nPO8}^2} - \overline{v_{nPO1}^2} \tag{3.53}$$

から

$$\sqrt{\overline{v_{nPix8}^2}}/8 = 243[\mu V_{rms}] \tag{3.54}$$

が求まる。これはノイズシミュレーションから求まる値である  $82\mu V_{rms}$  よりもかなり大きい値を示した。理由として考えられるのは画素周辺の電源やグランドライン、シリコン基盤からのノイズの混入が考えられる。これは、カラムアンプのアーキテクチャに差動ではなくシングルエンドを用いていくためである。もしくは、画素の信号はカラムに読み出すために長いメタル配線を通して読まれるために、これがアンテナとなって外部からの環境ノイズが信号に混入していると考えられる。

## 3.10 まとめ

本研究ではCMOSの機能回路を集積できるという特徴に注目し、画素信号を適応的にカラムで増幅することのできる、適応ゲインカラム増幅に基づくCMOSイメージセンサについて試作、検討を行った。イメージセンサの高画質化には信号飽和レベルを拡大する高照度側のダイナミックレンジの拡大と、ノイズレベルを低減する低照度側ダイナミックレンジを広げるの2通りの方法があり、主に後者に焦点を当てノイズレベルの低減を行った。高照度側のダイナミックレンジの拡大は、画素にブートストラップ効果を持たせることで飽和信号レベルを拡大した。低照度側のダイナミックレンジを拡大する手法は、カラムで信号を増幅することで増幅回路以降のノイズを相対的に小さく見せることでノイズ低減を行う。しかしながら、単純に

信号を増幅するのみであると高照度側のダイナミックレンジが低下するために、適応的に信号を増幅することでこれを抑制した。ノイズの PSD と回路の等価回路の伝達関数を用いたノイズ解析の結果、カラム増幅は増幅部以降のノイズを相対的に小さく見せることができるだけでなく、カラム増幅器自体が発生するノイズも低減できることを見いだした。

また、適応カラム増幅はチップ外部で A/D 変換を行った際のデジタルダイナミックレンジを等価的に拡大する機能も持つ。外部に 14bit の A/D を使用した場合、カラムで 8 倍に増幅された低照度の信号は等価的に 17bit のダイナミックレンジを持つことになり非常に高精度なデジタル演算が可能となる。そのため、デジタルノイズキャンセルにより、固定パターンノイズを  $50\mu V_{rms}$ 、ランダムノイズを  $263\mu V_{rms}$  と低ノイズ化に成功た。試作チップは、 $0.25\mu m$ CMOS イメージセンサ専用プロセスを用いて画素回路に埋め込みフォトダイオードを使用した。これにより、 $3.9V/lx\cdot s$  という高い感度と 18mV/sec(@60°C) で良好な暗電流特性となった。ダイナミックレンジは 1V 振幅で 71dB と CCD 並の低雑音を実現した。

# 参考文献

- [1] 松長、遠藤"CMOS イメージセンサのノイズキャンセル回路"映像情報メディア 学会報告書,vol.22,no.1,pp.7-11(Jan.,1998)

- [2] R.M.Guidash et al..,"A  $0.6\mu m$ CMOS pinned photodiode color imager technology,"in IEDM Tech. Dig.,1997,p.927

- [3] K.Yonemoto, H.Sumi, "A CMOS Image Sensor with a Simple Fixed-Pattern-Noise-Reduction Technology and a Hole Accumulation Diode," IEEE J.Solid-State Circuits, vol. 35, No. 12, pp. 2038-2043, Dec. 2000.

- [4] J. H. Fischer," Noise source and calculation techniques for switched capacitor filters," IEEE J. Solid-stage circuits," vol. SC-17, no. 4, pp.742-752, Aug. 1982.

- [5] C. A. Gobet,"Noise analysis of switched capacitor networks,"IEEE Trans. Circuits and Systems, vol. CAS-30, no. 1, pp. 37-43 (Jan. 1983).

- [6] 河合 信宏"CMOS イメージセンサのノイズ解析と低ノイズ化に関する研究", 静岡大学博士論文, Feb. 2005

- [7] C. A. Gobet, "Spectral Distribution of a sampled 1st-order lowpass filtered white noise," Electronics Letters, vol.17, no. 19, pp.720-719 Sept. 1981.

# 第4章

# 2重積分型カラム並列A/D変換器

## 4.1 はじめに

CMOS イメージセンサの画質の改善はイメージセンサからの信号をいかに低ノイズで読み出すことができるかにかかっている。原理的にノイズ帯域の狭いカラム [1] で信号を増幅するとノイズが低減できることに注目し、カラムで適応的に増幅をして帯域の広いセンサー出力でのノイズの耐性を高めたイメージセンサを3章で報告し [2]、カラムでの低ノイズ化の演算はノイズ帯域の観点から非常に有効なノイズ低減方法であることを実証した。しかしながら、センサチップから出力された帯域の広いアナログ信号を外部で A/D 変換しているためにその性能を十分発揮できていなかった。従って、帯域の狭い画素もしくはカラムにおいて A/D 変換を行うことで、支配的なノイズそのものを重畳しない方法でさらなる低ノイズ化を実現できることは容易に理解できる。この実現には、高精度かつ高分解能の A/D 変換器が必要不可欠である。

画素内に信号処理回路を設けて低い帯域、ピクセルレベルで A/D 変換をする方式 [3] [4] は画素内に比較器などの回路を集積することから、小面積化には不向きであることに加えて画素のバラツキや ADC の分解能不足による特性の劣化が顕著である。カラムに A/D 変換器を設けるとノイズ帯域が狭い状態で A/D 変換を行うことができ、量子化された後は原理的にノイズが重畳せず非常に有効である。しかしながら、近年報告されているカラムに A/D 変換器を搭載しているイメージセンサ [5]- [6] の分解能は 10bit から 11bit であり、十分なデジタルダイナミックレンジが得られていない。また、12bit の分解能を [7] が報告しているが、このセンサの実質的な精度は直線性誤差を考慮すると、10bit 程度であった。その理由は、画素単位で A/D 変換する方式に比べれば面積に余裕があるものの、依然としてカラム回路の横方向の幅は画素のサイズで制限されるため、使用できるトランジスタやキャパシタのサイズが制限され、高精度化、低ノイズ化が難しいためである。カラム 12bit の性能を満たす A/D 変換器を達成した報告 [8] がなされたのは最近である。

このような問題を抱えつつも、イメージセンサからの信号を低ノイズで読み出すには、ノイズ帯域の狭いカラムに回路を集積することが不可欠であり、回路的な工夫が要求される。このようなことから、カラムの回路で信号の演算を行い、なるべく小さな面積でノイズを低減する回路の開発が望まれる。

この章ではノイズ低減効果をさらに発展させて、低照度時のみでなく高照度時に

もノイズ低減効果を計った方式について述べる。時間領域での処理を有効に利用し、ランダムノイズならびに量子化ノイズを低減することで、従来のカラム A/D 変換器より高分解能デジタル値を出力可能な 2 重積分型カラム並列 A/D 変換器を提案する。 2 重積分型 A/D 変換方式は、他の章の方式に比較して低照度から高照度にわたり読み出し回路のランダムノイズと A/D 変換器の量子化ノイズを低減するため、高階調の画像を取得することが可能である。本方式は、入力信号のレベルによって適応的に回路の動作モードが変化することがないためにモードの切り替わりでの特性の変化に対する補正処理が不要なこともあげられる。

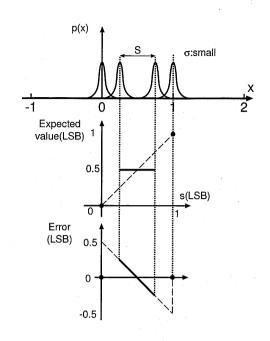

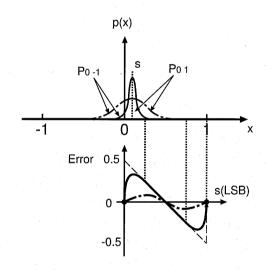

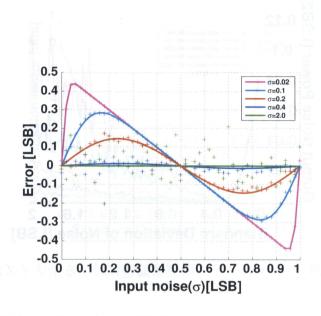

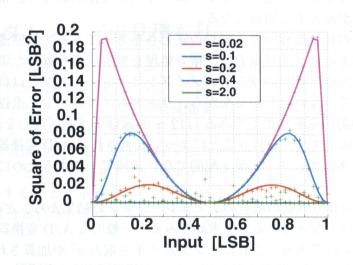

本 A/D 変換器は、粗い A/D 変換を行うインクリメンタル A/D 変換モードと、その後の信号追従・平均化モードをもつ。本論文は、特に信号追従・平均化モードにおけるランダムノイズと量子化ノイズの低減効果について、状態遷移図による解析を行い、シミュレーションによる検討をおこなった。特に、信号追従・平均化モードでは、センサの信号に、あるランダムノイズが重畳していた場合に、2 重積分型 A/D 変換器の量子化ノイズがランダムノイズのディザリングの効果により平均化され、量子化ノイズが低減されるとともに、入力信号に含まれるランダムノイズも平均化により低減されることが見いだせた。また、入力信号に含まれるランダムノイズはノイズ低減効果が最も発揮される 0.4LSB 付近のレベルであることをノイズ解析から計算した。以下に CMOS イメージセンサに集積する場合の全体の構成、2 重積分型 A/D 変換器の構成と動作、提案する量子化ノイズ低減効果の解析、およびシミュレーション結果について順次述べる。

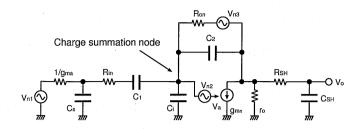

## 4.2 2 重積分型 A/D 変換器の構成

### 4.2.1 全体の構成

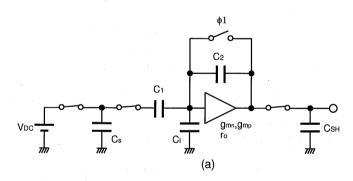

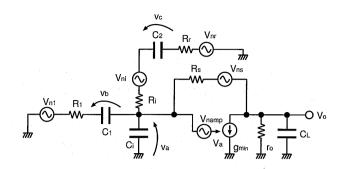

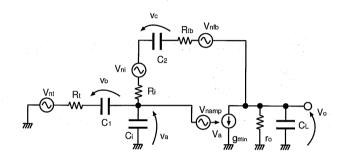

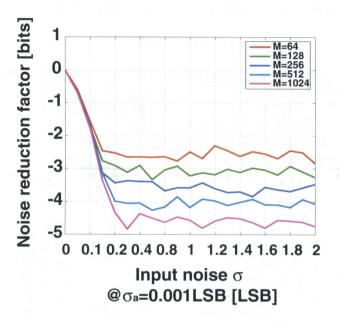

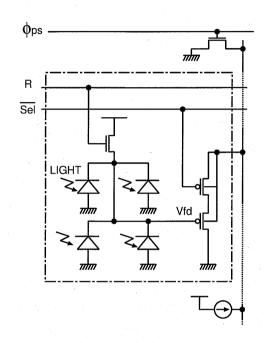

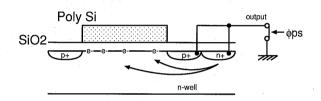

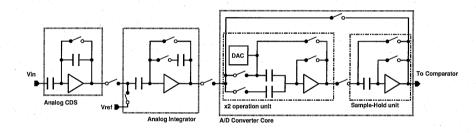

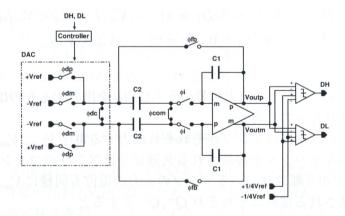

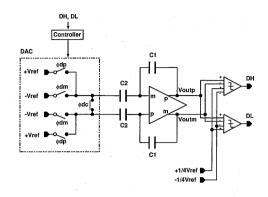

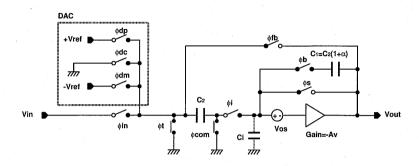

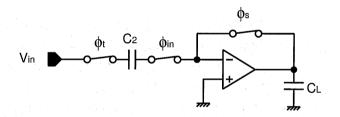

図 4.1 に提案する 2 重積分型 A/D 変換器を集積した、CMOS イメージセンサのブロック図を示す。この図で画素部は、4トランジスタ方式の APS(active-pixel sensor)を想定している。これと画素部のトランジスタによりソースフォロワのバッファが形成され、画素内の電荷検出部の電圧が読み出される。

垂直スキャナにより、受光部である画素の2次元イメージアレイの1列が信号 Sel により選択される。まず、画素部の電荷検出部の電荷を信号 R により初期化レベル (リセットレベル) にする。その信号がカラムに並列に読み出され、列並列に A/D変換されてリセット信号用レジスタに記憶される。次に、受光した信号を画素から読み出し、列並列に A/D変換して受光信号用レジスタに記憶する。最終的に、外部に出力する直前でリセット信号と受光した信号のデジタル値の差をとり出力する。これによって、画素部が発生するリセットノイズと固定パターンノイズをデジタル領域で除去している。また、その A/D変換の際、2 重積分動作により、画素部のソー

図 4.1: 2 重積分型 A/D 変換器を用いたイメージセンサのブロック図

スフォロワアンプを含む A/D 変換回路の発生するランダムノイズが低減される。

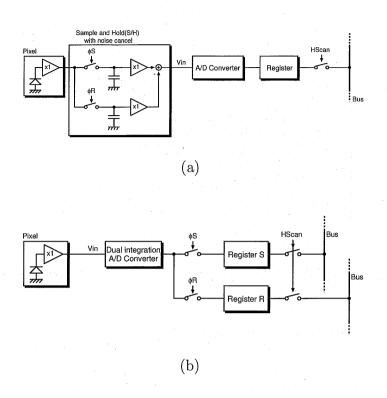

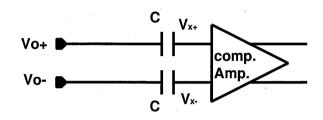

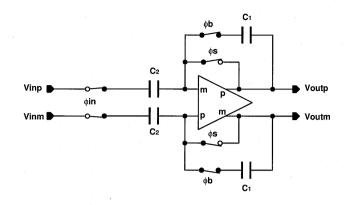

### 4.2.2 2 重積分型 A/D 変換器の構成

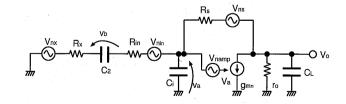

図 4.2(a) 及び (b) は、一般的なカラム A/D 変換器 (図 4.2(a)) と提案する 2 重積分型 A/D 変換器 (図 4.2(b)) における、垂直のスキャナでセンサの 1 ラインが選択された場合の 1 カラム分の回路図を示す。

図 4.2(a) の回路では、まず、画素からリセットレベルが画素部のバッファを介して読み出され、スイッチの制御信号  $\phi R$  によって S/H 回路に記憶される。続いて信号レベルが読み出され、同様に信号  $\phi S$  にてもうひとつの S/H 回路に記憶される。その差電圧がカラム A/D 変換器に入力されて A/D 変換が行われる。これらの動作からわかるように、A/D 変換器に入力される信号は画素のリセットレベルを基準にした信号変化量であり、相関二重サンプリング (corrlated double sampling, CDS) により画素部のリセットノイズと固定パターンノイズ (fixed-pattern noise, FPN) をキャンセルする。画素部のリセットレベルは画素部のトランジスタの閾値ばらつきが影響し、各画素毎に固定の値である。そのばらつきに加えて信号検出部は画素にリセット信号が入力される度にトランジスタの ON 抵抗による熱雑音が重畳し、リセット終了時にそのノイズレベルを記憶する。これは毎回違った電圧値を出力する。画素から信号レベルを出力する際は、リセットノイズが記憶されたリセットレベルを基準に、受光信号の情報を含む電圧値が同一の画素から出力されるため、両者の相関差分をとることで画素のリセットノイズと固定パターンノイズをキャンセルし、信号成分のみを取り出すことができる。

図 4.2: 画素からカラム出力までのカラムノイズキャンセル回路と (a) 一般的な A/D 変換器, (b)2 重積分型 A/D 変換器

一方、図 4.2(b) の提案する 2 重積分型 A/D 変換回路では、相関差分をとる機能は、A/D 変換後のデジタル値で行っている。図 4.2(a) の回路がアナログ領域で相関差分をとるのに対して、図 4.2(b) はデジタル領域で相関差分をとる。問題となるのは、デジタル領域で相関差分をとる場合、デジタルダイナミックレンジが十分でないと量子化誤差による影響が無視できなくなることである。しかし、後に述べるように、本方式でのデジタルダイナミックレンジは十分広いので、この問題は回避できる。

以上の CDS 動作によって、画素部のリセットノイズと固定パターンノイズはキャンセルされる。実際に読み出される信号には、読み出し回路が発生する熱雑音のランダムノイズが重畳する。図 4.2(a) の回路では画素のバッファアンプ、S/H 回路、A/D 変換器がランダム雑音の発生源になっている。一方、図 4.2(b) の回路は、画素のバッファアンプと A/D 変換器がランダム雑音の発生源である。このようなランダム雑音は、相関のある信号に対して多数回サンプリングして、平均化を行うことで低減が期待される。

図 4.2(a) の回路では、S/H 回路で相関差分をとる場合、画素からの経路がスイッチにより分断される。したがって後段の A/D 変換器で多重サンプルし平均化を行ったと仮定しても、S/H 回路のランダムノイズ低減効果はあるにせよ、画素回路のラ

ンダムノイズは低減できない。

一方、図 4.2(b) では画素の出力は、A/D 変換器に直接入力されており、2 重積分型 A/D 変換器により積分動作が行われているときも、画素からの信号経路は接続されたままである。したがって、提案する 2 重積分型 A/D 変換器で加算平均した場合には、画素で発生するランダムノイズも低減できることがわかる。

以上のことから、2 重積分型 A/D 変換器とデジタル領域での CDS 動作は画素から A/D 変換器までの全てのアナログ回路で発生するランダムノイズを低減することが でき非常に低ノイズ、高精度の A/D 変換器を実現できることがわかる。

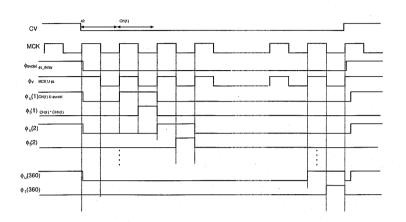

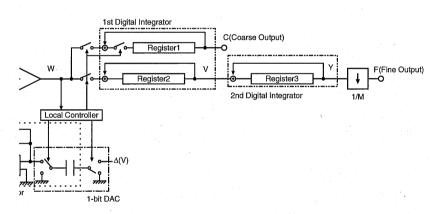

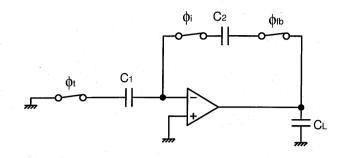

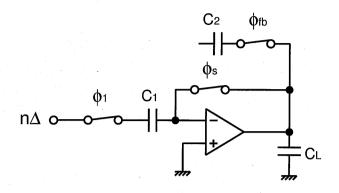

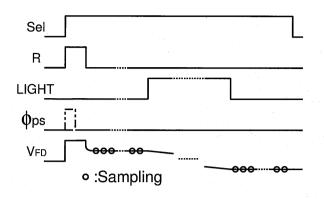

## 4.2.3 2 重積分型 A/D 変換器のモード

提案する 2 重積分型 A/D 変換器は、比較器 (コンパレータ)、アナログ積分器、2 つのデジタル積分器、1-bit D/A 変換器 (DAC) から構成される。図 4.3 に回路図を示し、その動作を図 4.4 に示す。この図では、入力レベルを 8.6LSB と仮定して動作を説明している。 本方式は、インクリメンタル A/D 変換を行うモード (IADC モー

図 4.3: 2 重積分型 A/D 変換器

ド) と、入力信号に追従する $\Delta$ 変調器の出力に平均値フィルタリングの処理を行う、信号追従・平均化処理モード (TA モード) からなり、各々のモードの出力が Coarse Ourput と Fine Output となっている。

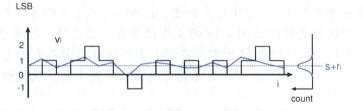

• インクリメンタル ADC モード (Incremental ADC mode) ここでは入力信号を粗く A/D 変換する。入力電圧がどのレベルにあるかを 1-bit DAC とアナログスイッチトキャパシタ (SC) 積分器によりサーチする。SC 積分器の出力は、最初 0 に初期化しておく。SC 積分器の出力はクロックが与えられるたびに、 $\Delta$  のステップで出力がインクリメントされるように設定しておく。SC 積分器の出力が入力電圧を越えた次の時刻 t=LT でコンパレータの出力が反転する。その瞬間までのクロック数を A/D 変換値とし、それを Register1 に

図 4.4: 入力に  $V_{in}=8.6 \mathrm{LSB}$  を仮定した場合の 2 重積分型  $\mathrm{A/D}$  変換器の動作

記憶する。その後、カラム全ての回路が IADC モードを終了する時刻 t=NTまで動作を停止 (アイドリング状態) する。

● 信号追従・平均化処理モード (Tracking and averaging mode) 一般的なインクリメンタル ADC では、以上の動作で処理が完結する。本提案の方式では、画素部の出力が一定の値を出力し続けている特徴に注目し、△変調の動作によって入力信号に追従させながら量子化し、その出力に平均化処理を加えることによって、量子化ノイズの低減による分解能の向上とランダムノイズの低減をはかるでものある。時刻 t = NTでデジタル積分器を2段に接続し、TAモードの動作に移行する。モード切り替わり時に接続される、両デジタル積分器の初期値は0とする。IADCモード終了時の入力信号とSC積分器の出力の差は0から1LSBの範囲の電圧値であり、この信号はランダムノイズによって真値を中心に振動している。もし、ノイズがまったく重畳していないとするならば、デジタル積分器の初段は0~1を繰り返し出力しその加算平均は0.5LSBとなるであろう。ノイズが加わっていることで、入力信号の真値が1LSBの中でどのような値をとるかによって、デジタル積分器の初段の出力がとる0と1の頻度に違いが生じ、2段目の積分器で平均化処理を行うことで、1LSB以下の精度で入力信号の真値を推測できる。すなわち、分解能が向上する。

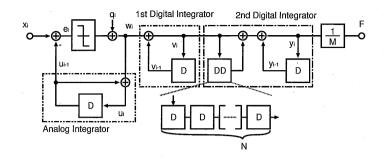

## 4.3 2 重積分型 A/D 変換器の動作

2 重積分型 A/D 変換器の TA モードの動作を詳しく検討する。図 4.5 に TA モード 時の A/D 変換器の動作を表すブロック図を示す。初段のデジタル積分器は  $\Delta$  変調器の動作によって、その出力の平均は 0 から  $\Delta$  の範囲に存在する。また、これは M 回

図 4.5: Block diagram of the dual-integration-type ADC

動作した後にリセットがかかるため、厳密には不完全積分器であるが、実際にとる出力はコードとして、初期値である0付近から大きく外れることはない。確率的に0もしくは1で積分が終了していることが多いため、M回動作の後に初期化をしたとしても完全積分器とみなすことに問題はない。2段目の積分器は初段の積分器の出力をM回加算し毎回初期化するので、完全積分器とはみなせず、不完全積分器となる。図4.5において、i番目の時刻における内部変数は、以下のように表すことができる。

$$e_i = x_i - u_{i-1} (4.1)$$

$$w_i = e_i + q_i \tag{4.2}$$

$$u_i = w_i + u_{i-1} \tag{4.3}$$

$$v_i = w_i + v_{i-1} (4.4)$$

$$u_0 = v_0 = 0 (4.5)$$

ここで $x_i$  は入力信号、 $q_i$  は量子化ノイズ、 $u_i$  はアナログ信号の積分器出力、 $w_i$  は比較器の出力、 $v_i$  は初段のデジタル積分器の出力、 $e_i$  は予測誤差である。以上の式から、

$$u_i = x_i + q_i (4.6)$$

$$v_i = x_i + q_i \tag{4.7}$$

が求まる。これからこのアナログ積分器の出力  $u_i$  はデジタル積分器の出力  $v_i$  に等しく、また、入力信号を A/D 変換した値であることがわかる。2 段目のデジタル積分器で、M 回の加算を行って平均値を求めるとすると

$$F = \frac{1}{M} y_M = \frac{1}{M} \sum_{i=1}^{M} v_i \tag{4.8}$$

$$= \frac{1}{M} \sum_{i=1}^{M} (x_i + q_i) \tag{4.9}$$

入力信号 $x_i$ は真の入力信号s(直流)にランダムノイズ信号 $r_i$ が加わったものとすると

$$F = \frac{1}{M} \sum_{i=1}^{M} (s + r_i + q_i)$$

(4.10)

$$= \frac{1}{M} \left( \sum_{i=1}^{M} s + \sum_{i=1}^{M} (r_i + q_i) \right) \tag{4.11}$$

$$= s + \frac{1}{M} \left( \sum_{i=1}^{M} (r_i + q_i) \right) \tag{4.12}$$

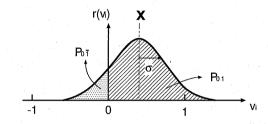

となる。これより2段目のデジタル積分器によって、平均化処理によりランダムノイズと量子化ノイズの低減が期待される。量子化ノイズによる雑音電力 $N_a$ は、図 4.6

図 4.6: 量子化雑音の確率密度関数

のように、量子化ステップ  $\Delta$  (1LSB) で一様な確率密度をもつとして、一般に

$$N_q = \int_0^\Delta (\Delta - \frac{\Delta}{2})^2 p(x) dx = \frac{\Delta^2}{12}$$

$$\tag{4.13}$$

と求めることができる。もし、この量子化ノイズが完全にランダムな現象であれば、M回の平均化処理により電力が1/Mになることが期待される。しかし実際は、そのようにはならず、そのノイズ低減効果は含まれるランダムノイズに大きく依存する。このようなランダムノイズによる分解能の向上はディザリング処理として知られている。後の節において本提案方式における量子化ノイズ低減効果を解析する。

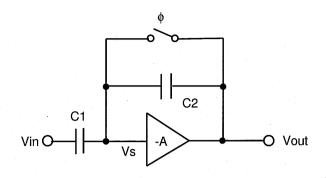

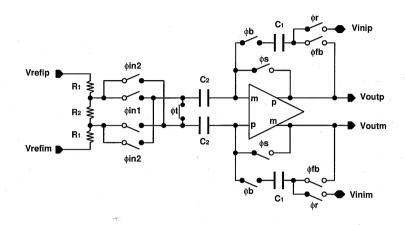

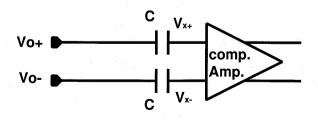

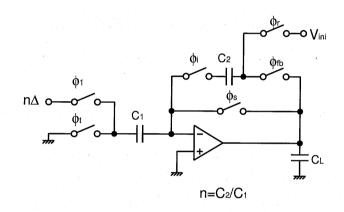

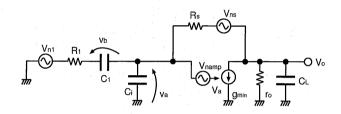

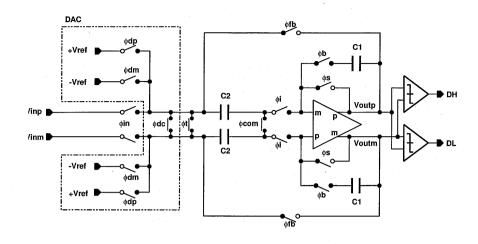

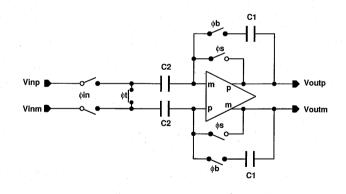

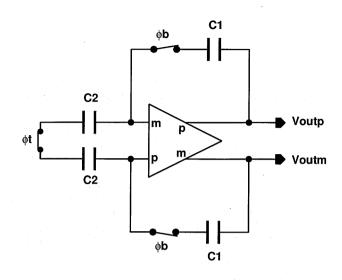

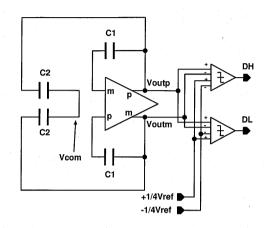

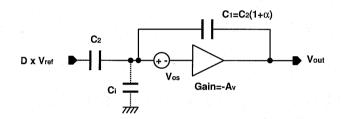

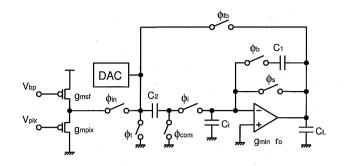

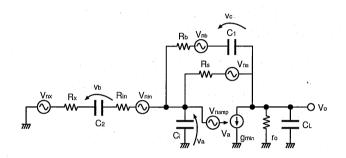

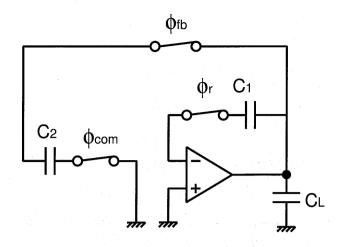

#### 4.3.1 アナログ積分器と 1bit DAC の構成

本方式に使用されるアナログ積分器と 1bitDAC は、1 クロックあたり  $\pm \Delta$  の正確な電圧を出力することを期待され、これが A/D 変換器の性能を左右する。これはアナログ積分器が比較器で比較される参照電圧を発生させているために、参照電圧の精度がそのまま A/D 変換器の精度に影響するからである。本方式で用いる単位ステップ電圧  $\Delta$  はフルスケールを 1.024V で A/D 変換のステップ数を 10bit(1024) にするために 1mV を想定している。図 4.3 に示したように外部から 1mV の電圧を直接入力

することでも実現できるが、参照電圧としてこの値は小さすぎるためにノイズに対する耐性を持たせる工夫が必要である。

実際にノイズに耐性を持たせる工夫をした回路を図4.7に示す。厳密にいえば、アナログ積分器と1bitDACは回路上で分離ができず、図に示す回路全体で1bitDACとアナログ積分器の機能を共有している。実際に行ったノイズ対策は、

図 4.7: 1bitDAC とアナログ積分器の構成

- 差動アーキテクチャの採用

- 容量比による演算でノイズ耐性の向上

- 抵抗比による演算でノイズ耐性の向上

である。差動アーキテクチャは、入力のコモンモードに対して出力が変化しないので、ノイズ耐性が必要な回路に広く採用されているアーキテクチャである。容量比による演算は、スイッチトキャパシタで行う。図中の入力容量  $C_2$  と帰還容量  $C_1$  の比で決定する。実際には  $C_1/C_2=16$  で入力側にある容量  $C_2$  の片側に入力される電圧の 1/16 が  $V_{outp}$ ,  $V_{outm}$  に出力される。

入力電圧は抵抗  $R_1$ ,  $R_2$  により分圧されたものが入力される。この電圧は、抵抗と入力容量  $C_2$  により CR 時定数でチャージされるが、セットリングが十分間に合う抵抗値に設定してある。実際には  $R_1/R_2=31/2$  の値を取り、入力信号  $V_{refip}$ ,  $V_{refim}$  の差の 1/32 の電圧が容量に蓄積されることになる。

逆算すると、 $\Delta = V_{outp} - V_{outm} = 1 mV$  の条件を満たすには入力信号の差分として  $V_{refip} - V_{refim} = 512 mV$  の電圧を入力する必要がある。入力のリファレンスとして外部から 512 mV を正確に入力することは、1 mV の基準信号を外部から正確に入力することに比べて極めて容易である。このため、入力信号の誤差とノイズに対して耐性が向上する。

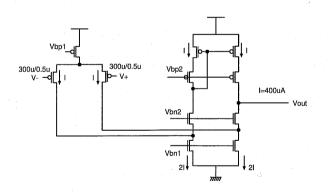

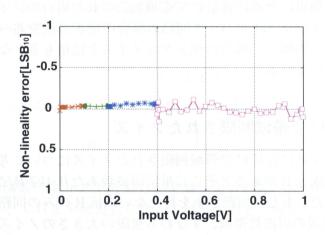

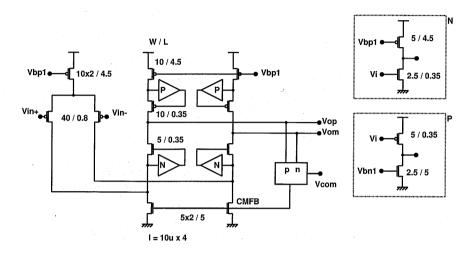

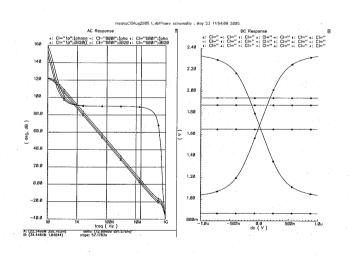

### 4.3.2 増幅器の構成と特性

実際に回路で使用する増幅器の構成を述べる。高分解能の A/D 変換器を実現するために、アナログ積分器は精度の高い正確な参照電圧を発生する必要がある。そのために、増幅器には利得の高い増幅器アーキテクチャである、折り返しカスコード方式にゲインブーストを行ったものを使用する。実際の回路図を図 4.8 に示す。また、

図 4.8: ゲインブースト折り返しカスコード増幅器

この増幅器をシミュレーションにより確認した。その特性を図4.9に示す。ボード線

図 4.9: ゲインブースト折り返しカスコード増幅器の特性

図より、負荷容量が 0.6pF から 1pF の間では安定して動作することを確認できる。なお、この特性はコモンモードフィードバックに理想の素子の電圧制御電圧源を使

図 4.10: 比較器の構成

用し、バイアス源などは実際にトランジスタを用いて構成してシミュレーションを 行った。

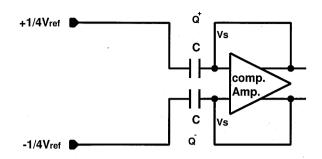

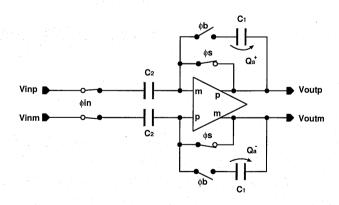

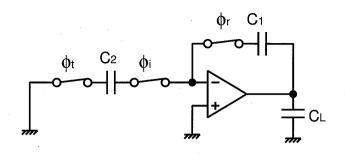

#### 4.3.3 比較器の構成

入力信号と参照電圧を比較する比較器は、高精度のものを使用する必要がある。2 重積分型 A/D 変換器のアーキテクチャが比較レベルの冗長性を持たず、入力信号を 1LSB 刻みで正しく判断する必要があるためである。比較器の構成を図 4.10 に示す。比較器は入力にキャパシタ C、信号を増幅するプリアンプ、プリアンプの出力を増幅しつつラッチするラッチ回路、入力が"11"で安定の S-RFF と各種のスイッチで構成される。入力信号の  $Vo\pm$  は画素からの出力信号が接続され、 $V_{ref}\pm$  はアナログ積分器が出力する参照電圧が接続される。

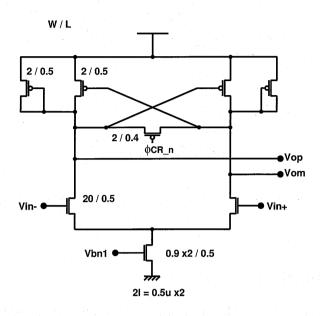

#### プリアンプの構成

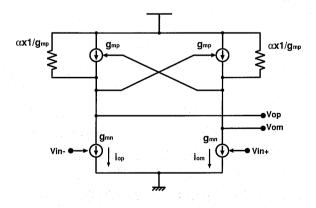

比較器の内部回路であるプリアンプの構成を図 4.11 に示す。入力信号にある程度 の差がある状態でスイッチ  $\phi_{CR\_n}$  が OFF すると、出力の  $V_{op}$  と  $V_{om}$  が電源電圧もしくは電流源トランジスタと入力トランジスタのオーバードライブ電圧の合計の電圧 付近のどちらかが出力される。このアンプのゲインを求めてみる。小信号での等価 回路を 4.12 に示す。PMOS 側のドレインとゲートが接続され、ダイオード接続の構成をとる。この構成での出力側から見たインピーダンスは、ダイオード接続をして いるトランジスタのインピーダンスがソース接地をしている NMOS と PMOS トランジスタの出力抵抗よりも約 2 桁低いために、等価的に  $\alpha \cdot 1/g_{mp}$  となる。この等価 回路で出力側の電流  $i_{om}, i_{op}$  はそれぞれ

$$i_{om} = g_{mn} \cdot V_{in} = g_{mp}(-V_{op}) + \alpha \frac{-V_{om}}{1/g_{mp}}$$

(4.14)

$$i_{op} = g_{mn} \cdot V_{in} = g_{mp}(-V_{op}) + \alpha \frac{-V_{op}}{1/g_{mp}}$$

(4.15)

図 4.11: 比較器のプリアンプの構成

図 4.12: 比較器のプリアンプの等価回路

図 4.13: 比較器のラッチ回路

となり、これらからこのアンプの増幅率を求めると

$$A_v = \frac{V_{om} - V_{op}}{V_i^+ - V_i^-} = \frac{g_{mn}}{g_{mp}} (\frac{1}{1 - \alpha})$$

(4.16)

ここで PMOS 側のトランジスタのサイズを同じにすると、係数である  $\alpha=1$  となるので  $\frac{1}{1-\alpha}=\infty$  となり、ゲインが無限大のアンプになる。実際に作成する際にはサイズばらつきなどの影響を受けて無限大にはならない。

一般的に、比較器のプリアンプはゲインを持たせるよりも比較演算のスピードを 重視するためにゲインを無限大にすることはあまりない。

しかしながら、本方式は 1LSB を正確に判定する必要があるので、あえてゲインを無限大になるよう設計している。これにより、次段にラッチ回路が付いた状態で入力信号の差が  $50\mu V$  まで正確に比較できることを確認している。

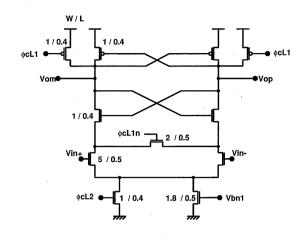

#### ラッチ回路の構成

図 4.13 に比較器の内部回路であるラッチ回路を示す。ラッチ回路の基本はインバーター 2 段の数珠つなぎである。インバータが動作しないときは  $\phi_{cL2}$  により電源から切り離され、 $\phi_{cL1}$  により出力が"1"(電源電圧)に固定される。また、その時  $\phi_{cL1n}$  により入力トランジスタのドレインに残留する電荷を消去し信号の履歴に回路が影響されないようにする。 $\phi_{cL2}$  により電源から完全に切り離され、回路が完全に浮遊状態になると次に動作するスタートアップに時間がかかることなどから、 $V_{bn1}$  によりわずかに電流を流す。

### 4.3.4 比較器の動作

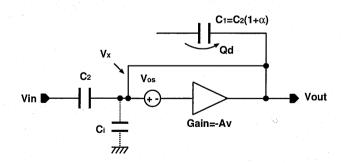

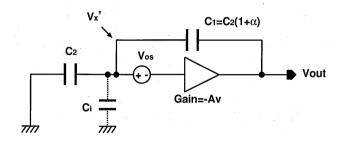

以上の回路を用いた比較器の動作を説明する。まず、比較器の入力には  $\phi_{ci2}$  によりアナログ積分器からの電圧が入力さる。その時プリアンプの入出力は  $\phi_{cs}$  によりショートされている。この時、アンプのショート電圧  $V_s$  と入力電圧とで決まる電荷が容量 C に蓄積される。初期状態での回路の状態を図 4.14 に示す。入力側の容量 C

図 4.14: アナログ積分器からの信号をサンプルしている時の回路の状態

に蓄積される電荷をそれぞれ $Q^+,Q^-$ とすると、

$$Q^{+} = C(V_{ref+} - V_s) (4.17)$$

$$Q^{-} = C(V_{ref-} - V_s) (4.18)$$