#### 科学研究費助成事業 研究成果報告書

平成 27 年 6 月 2 1 日現在

機関番号: 13801 研究種目: 基盤研究(B) 研究期間: 2012~2014

課題番号: 24300018

研究課題名(和文)革新的解析手法による高速伝送信号の多並列指向型超高性能 CAEシステム

研究課題名(英文)Highly-parallel and high-performance CAE system based on revolutionary analysis method for high-speed signaling

#### 研究代表者

浅井 秀樹 (Asai, Hideki)

静岡大学・電子工学研究所・教授

研究者番号:40175823

交付決定額(研究期間全体):(直接経費) 14,000,000円

研究成果の概要(和文):集積化技術の進歩に伴い,電子システムの高密度化,高速化が著しく進んだ.それに伴い,電源,信号の品質保証問題が深刻となっており,設計時の回路の動作検証の重要性が増している.従って,詳細なモデル化とその効率的なシミュレーション技術が強く求められている. 本研究では,効率的な回路シミュレーション手法の提案とGPU付きPCクラスタによる多並列シミュレーションにより, 世界最高クラスの高速CAE (Computer-Aided Engineering)システムを構築した.

研究成果の概要(英文): With the progress of integration technology, high-density and high-speed electronic systems have been developed. As a result, the way how to guarantee the quality of power/signal has become very important and the some kind or another novel modeling and verification methodologies have been demanded.

In this research, an efficient simulation method has been proposed and the CAE (Computer-Aided Engineering) system composed of the PC cluster with GPUs (Graphics Processing Units) has been developed, which has the world record class of performance.

研究分野: 電子情報システム

キーワード: 回路とシステム シグナル・インテグリティ パワー・インテグリティ 大規模シミュレーション 並列計算 CAE 高速信号 HPC

## 1.研究開始当初の背景

電子機器は動作時に,ノイズや信号遅延,電磁干渉といった種々の影響を受ける.そのため,製品設計ではIC(集積回路)や回路板,筐体を含めた協調設計が必要となっている.製品設計段階で考慮しなければならない様々な問題のうち,特に,電源/グラウンドの電圧や配線上の高速伝送信号の品質,いたではである。そしてする。そのですがではであり、欧米ではCAE(Computer Aided Engineering)や物理現象のシミュレーション技術,東アジアではモデル化の研究はしからように世界規模で行われている.

本研究課題は CAE 技術に該当し,特に 回路解析の高速化に注目している.多くの電 子機器内に備え付けられている電子回路は、 高速動作するスイッチング素子を有してお り,このスイッチング素子から発生するノイ ズは電源/グラウンド層に回りこむ .この回り 込んだノイズは,本来なら一定であるはずの 電源/グラウンド層の至る所で電位を変化さ せ,電子回路を誤動作させる要因となる.そ のため ,製品設計時には電源/グラウンド層を 詳細にモデル化し解析することが求められ る.しかし,電源/グラウンド層は膨大な数の 素子(抵抗,容量,誘導素子等)によってモ デル化され,スイッチング回路を含めた回路 網は大規模となる.このような解析対象が与 えられた場合,世界標準とされる回路シミュ レータ SPICE(引用文献 )では大規模な非 線形連立方程式を解くことになる. そして / Newton 法に基づく差分により求まった大規 模連立方程式を LU 分解法により解析する. その際、SPICE シミュレータでは大規模な行 列演算が要求されるため,非常に多くの計算 機資源を必要とし,解析結果を実用的な時間 で得ることが事実上困難となっている.この ような問題を解決するために、SPICE シミュ レータよりも劇的な高速な解析手法が求め られている.

## 2.研究の目的

集積化技術の進歩に伴い,電子システムの高密度化,高速化が著しく進んだ.その結果,設計段階で高速伝送信号の振る舞いの正確な把握が重要となってきた.そのためには,詳細にモデル化された回路網を解析することになるが,一般的に,詳細モデルは膨大な数の抵抗や容量,誘導素子等によってモデル化される.このような回路モデルは SPICEシミュレータで解析し,実用的な時間で解析結果を得ることが困難である.これは,SPICEシミュレータが既存の数値解析手法に基づいているおり,非常に多くの計算機資源が要求されるためである.

このような多量の計算機資源を要求する 大規模問題に対して,近年, PC クラスタや GPU (graphics processing unit)を用いる多並列シミュレーション技術が注目されており、様々な分野で活用されている.しかし、SPICE シミュレータで用いられている数値解析手法は高並列計算に適しておらず、PCクラスタや GPU を利用することによる画期的な高速化の実現は困難である.そのため、既存の数値解析手法とは異なり、高並列計算に適した数値解析手法を開発し、多並列シミュレーション技術を適用することが必要となる.

本研究室では,これまでに,画期的な回路/電磁界の数値解析手法を開発してきた(引用文献 ).そこで,本研究では新しい独自の解析アルゴリズムを多並列指向型に改変し,アルゴリズム,ハードウェア両方式の優位性を両立させることで,世界最高性能のパワー/シグナル・インテグリティ検証システムに挑戦する.

#### 3.研究の方法

近年,提案された一変数型蛙飛び手法(引 用文献 ) に対して,強結合部をブロック化 するブロック型蛙飛び手法を新たに提案し てきた(引用文献).この手法は,強結合 多導体や電源/グラウンド層を含む回路の解 析に対して、SPICE シミュレータと比べて二 桁程度高速である.このブロック型蛙飛び手 法に対して,スイッチング回路のような非線 形能動素子を扱うためのブロック型非線形 蛙飛び手法へと改良を行う.通常,非線型連 立方程式を解く場合には,一時間ステップご とに非線形連立方程式の解法を適用するこ とになるため、SPICE シミュレータに対する 蛙飛び手法の優位性を失うと考えられる. そ こで,本研究では,非線形能動素子をそれに 対応するブロック内に含ませることで,一般 性を失うことなくブロック型蛙飛び手法の 適用を可能にする、このとき、非線形能動素 子を含むブロックは全ての状態変数と比べ るとごく小数の状態変数で構成される非線 形連立方程式を解くことになり、SPICE に対 する優位性を失うことがないと考えられる.

また、蛙飛び手法に多並列シミュレーション技術を適用することで、基となる手法自体の高速化を検討する.特に、大規模な物理現象シミュレーションで用いられるようになってきたGPUへの適用を検討する.GPUは、CPUと比べて非常に高速であり、高速化に大きく貢献すると考えられるが、GPUボード上のメモリ容量は大規模問題の解析には大分とはいえない.そこで、GPU付き PC クラスタを構築し、考案した手法を多並列型指向に改編、多並列計算機構上に実装する.以上の方法で、世界最高性能のパワー/シグナル・インテグリティ検証システムに挑戦する.

#### 4. 研究成果

本研究では,新たな回路解析手法の開発と解析手法の多並列シミュレーション技術の

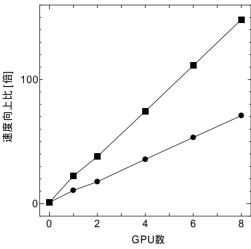

## —◆— 速度向上比(倍精度型浮動小数点) —■— 速度向上比(単精度型浮動小数点)

図 1. 蛙飛び手法の多並列シミュレーションによる高速化の推移.

適用の二つを軸に行われた.回路解析手法の 開発では、ブロック型蛙飛び手法の非線形能 動回路への対応,ベクトルフィッティングを 用いた回路合成,陽的かつ無条件安定な手法 を開発し,国内研究会および国際会議におい て発表した.ブロック型蛙飛び手法の非線形 能動回路への対応では,非線形能動回路に対 応したブロック構造を用いることで解析可 能にした.これは,従来手法であれば大規模 な非線形連立方程式を解くのに対して, 非線 形能動回路を含むブロックのみの非線形連 立方程式を解くことになるため, 行列サイズ が小さくなり,きわめて効率的に解析できる. また,マクロモデル合成では周波数応答から 求めた伝達関数より,等価回路網の抽出を可 能にし、陽的かつ無条件安定な手法では、よ リ効率的に解析できる可能性のある数値解 析手法を提案した.また,派生手法として提 案した節点解析法と緩和法を基にした節点 ブロック緩和法については,電子情報通信学 会の論文誌に掲載された.

次に,多並列シミュレーション技術につい ては,蛙飛び手法と,HIE-FDTD法について多 並列シミュレーションへと展開した. HIE-FDTD 法(引用文献 )は,蛙飛び手法に 類似した数値解析手法であり,多並列シミュ レーションに適していることが判明し,それ を開発,検証した.上記の二手法は,従来手 法よりも高速に解析できるが, 多並列シミュ レーションへと展開することにより,従来手 法と比べて高速な蛙飛び手法のさらなる高 速化を実現した.ここで,蛙飛び手法の多並 列シミュレーション時の解析速度の推移を 図 1 に示す.これは, CPU で解析した場合の 速度を 1 とし, GPU の数を最大 8 個用いた時 に何倍高速に解析できるかを示している. GPU 数が 0 のときが CPU で蛙飛び手法を実行 した場合,それ以外はGPUを用いた多並列シ ミュレーションである .図 1 より ,8 個の GPU を用いた場合には , 従来手法よりも高速な解析手法をさらに二桁程度高速化できていることが分かる . この多並列シミュレーション技術についても , 国内研究会および国際会議で発表した .

提案した解析手法らは,集積回路や回路基板の解析を劇的に高速化しており,電源/グラウンド層やスイッチング回路のノイズ解析が実用的な時間で解析することを可能にしていると考えられる.しかしながら,電子回路設計のさらなる効率化を考えた場合,より大規模な問題や電子回路の最適化を含めた回路解析技術の発展が必要であると考えられる.

## <引用文献>

L.W.Nagel and D.O.Pederson "SPICE-Simulation Program with Integrated Circuit Emphasis", Memo no.ERL-M382, Electronics Research Laboratory, Univ. of California, Berkeley, April 1973.

浅井秀樹, "高速電子設計のための SI/PI/EMI シミュレーション技術 - 過 去、現在、そして未来 - ", Fundamentals Review, Vol.5, No.2, pp.146-154, 2011 年1月.

J.E.Schutt-Aine: "Latency Insertion Method (LIM) for the Fast Transient Simulation of Large Networks", IEEE Trans. Circuits Syst.-I, Vol.48, No.1, pp.81-89, 2001.

T. Sekine and H. Asai "Block Latency Insertion Method (Block-LIM) for Fast Transient Simulation of Tightly Coupled Transmission Lines", IEEE Trans. Electromag. Compat., Vol.53, No.1, pp.193-201, 2011.

Masaki Unno and Hideki Asai, "HIE-FDTD Method for Hybrid System with Lumped Elements and Conductive Media," IEEE Microwave Wireless Compon. Lett., vol.21, no.9, pp.453-455, Sept. 2011.

#### 5 . 主な発表論文等

(研究代表者、研究分担者及び連携研究者に は下線)

# 〔雑誌論文〕(計2件)

浅井秀樹, 井上雄太, 關根惟敏, "高速三次元電磁界・回路シミュレーション技術の現状と将来展望-アルゴリズムと並列計算の観点から-",電子情報通信学会 基礎・境界ソサイエティ Fundamentals Review, 査読無, vol.7, no.3, pp.197-209, 2014年1月.

高崎貴大,<u>關根惟敏</u>,<u>浅井秀樹</u>, 節点ブロック緩和法を用いた不均一な多導体伝

送線路の高速過渡解析 ",電子情報通信学会論文誌(C), 査読有, vol.J96-C, No.6, pp.114-121, 2013 年 6 月.

# [学会発表](計22件)

<u>浅井秀樹</u>, "三つの I(SI/PI/EMI)- 昨日、今日、そして明日 - ",電子情報通信学会総合大会,2015年3月12日,立命館大学(滋賀県草津).

<u>浅井秀樹</u>, "次世代 SI/PI/EMI シミュレーション技術",電子情報通信学会総合大会, 2015 年 3 月 10 日,立命館大学(滋賀県草津).

<u>浅井秀樹</u> , " チップ・パッケージ・ボード・筐体協調設計のためのSI/PI/EMIシミュレーション技術とその活用 マルチドメイン・シミュレーション ", 信学技報, Dec.2014, 静岡大学(静岡県浜松).

井上雄太,浅井秀樹,"マルチGPU LIM を用いた大規模回路網の高速過渡解析"信学技法, vol.114, no.381, pp.7-13, EMCJ2014-75,2014年12月19日,静岡大学(静岡県浜松).

Yuta Inoue and Hideki Asai, "Fast Circuit Transient Simulation based on Multi-GPU LIM",第16回高柳シンポジウム, Nov. 12 2014,静岡大学(静岡県浜松).

<u>Hideki Asai,</u> "Toward Reduction and Optimization of Common-mode Noise for Automotive EMC Design", Proc.EPEPS2014, Oct. 2014, Portland, OR, USA.

Hideki Asai, "Advanced Modeling and Simulation Techniques for 3-D SI/PI/EMI Design", Proc. ICDREC, AVIC/4S 2014, Oct. 2014, Ho Chi Minh, Vietnam.

<u>Hideki Asai</u>, "SI/PI/EMI Issues and Exploitation of CAE in High Speed Electronic Design", Proc. IEEE EMC2014, Aug. 4 2014, Raleigh, NC, USA.

Yuta Inoue and Hideki Asai, "Accelerating the Large-Scale Simulation of Power Distribution Networks by Using the Multi-GPU LIM", Proc. IEEE EMC 2014, pp. 861-865, Aug. 7 2014, Raleigh, NC, USA.

Yuta Inoue and Hideki Asai, "Multi-GPU HIE-FDTD Method for the Solution of Large Scale Electromagnetic Problems", Proc. IEEE EDAPS2013, pp.126-129, Dec. 13 2013, 東大寺総合文化センター(奈良県奈良).

<u>Hideki Asai</u>, "Locally Implicit Block Leapfrog Scheme for PDN Simulation ",Proc. IEEE ICEAA2013 , pp.847-850 , Sep. 12-2013 , Torino , Italy.

Yuta Inoue, Hideaki Muraoka, Hideki Asai, "Efficient Electromagnetic Simulation of Multi-Layered PCB with CMOS Inverter by Using HIE/C-FDTD Method", Proc. URSI AP-Rasc 2013, Sep. 6 2013, Taipei, Taiwan.

Daisuke Honda, <u>Tadatoshi Sekine</u>, and <u>Hideki Asai</u>, "Macromodeling and Circuit Simulation of High-Speed Interconnects Based on Vector Fitting and Equivalent Circuit Synthesis", Proc. NCSP 2013, pp.484-487, Mar. 6 2013, Hawaii, HI, USA.

Norio Nishizaki, <u>Tadatoshi Sekine</u>, and <u>Hideki Asai</u>, "An Explicit and Unconditionally Stable Finite Difference Scheme for the Fast Transient Analysis of a Power Distribution Network", Proc. IEEE EDAPS 2012, pp.26-29, Dec. 10 2012, Taipei, Taiwan.

Yuta InoueandHideki Asai, " FastFullwaveSimulationBasedonParallel-DistributedHIE-FDTDMethod ",Proc.IEEEAPMC2012 ,pp.1253-1255 ,Dec. 7 2012 ,Kaohsiung, Taiwan.

本多大介、<u>關根惟敏</u>、<u>浅井秀樹</u>, " 伝送線路特性のベクトルフィッティングによる有理関数近似と等価回路合成",デザインガイア 2012 ,信学技法,vol.112,no320,pp.189-194, VLD2012-92,2012 年 11月 28日,九州大学百年講堂(福岡県福岡市).

西崎統大, <u>關根惟敏</u>, <u>浅井秀樹</u>, "陽的かつ無条件安定な手法による電源分配回路網の高速過渡解析", デザインガイア2012, 信学技法, vol.112, no320, pp.219-224, VLD2012-97, 2012 年 11月28日, 九州大学百年講堂(福岡県福岡市).

井上雄太, 關根惟敏, 浅井秀樹, "次世代回路設計技術に向けた高速 SI/PI/EMI シミュレータの開発", JIEP 修善寺ワークショップ, 2012 年 10 月 19 日, ラフォーレ修善寺(静岡県伊豆).

<u>Tadatoshi Sekine</u> and <u>Hideki Asai</u>, "Nonlinear Block-Type Leapfrog Scheme for the Fast Simulation of Multiconductor Transmission Lines with Nonlinear Drivers and Terminations", Proc. EPEPS2012, pp.284-287, Oct. 22 2012, Tempe, AZ, USA.

Hideki Asai, "Advanced PI/SI/EMI

- Simulation Techniques Based on Leapfrog Scheme", Proc. EMC Europe 2012, Sep. 17 2012, Roma, Italy.

- ② Takahiro Takasaki, <u>Tadatoshi Sekine</u>, and <u>Hideki Asai</u>, "Fast Transient Analysis of Multiconductor Transmission Lines Using Nodal Block Relaxation (NBR) Method ", Proc. ITC-CSCC2012, Jul. 17 2012, 札幌国際会議場(北海道札幌).

- ② 高崎貴大、<u>關根惟敏</u>,<u>浅井秀樹</u>,"節点 ブロック緩和法を用いた多導体伝送線 路の高速シミュレーション",信学技法, vol.112, no.113, pp.81-85, CAS2012-15,2012年7月3日,京都リサーチパー ク(京都).

# 6.研究組織

(1)研究代表者

浅井 秀樹 (ASAI, Hideki)

静岡大学・電子工学研究所・教授

研究者番号: 40175823

## (2)研究協力者

長谷川 孝博 (HASEGAWA, Takahiro)

静岡大学・基盤情報センター・准教授

研究者番号: 40293609

井上 雄太 (INOUE, Yuta)

静岡大学・学術研究員

研究者番号: 70538024

關根 惟敏 (SEKINE, Tadatoshi)

日本学術振興会・特別研究員

研究者番号: 00765993